## GRAPHIC OLED MODULE SPECIFICATIONS

| Crystalfontz Model Number | CFAL25664A-Y-B1                                        |

|---------------------------|--------------------------------------------------------|

| Hardware Version          | Version A, April 2010                                  |

| Data Sheet Version        | Version 1.0, April 2010                                |

| Product Pages             | http://www.crystalfontz.com/product/CFAL25664AYB1.html |

## Crystalfontz America, Incorporated

12412 East Saltese AvenueSpokane Valley, WA 99216-0357Phone:888-206-9720Fax:509-892-1203Email:techinfo@crystalfontz.comURL:www.crystalfontz.com

## **REVISION HISTORY**

|            | HARDWARE                                    |

|------------|---------------------------------------------|

| 2009/04/07 | Current hardware version: vA<br>New module. |

| DATA SHEET        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2010/04/09        | <ul> <li>Current Data Sheet version: 1.0</li> <li>Since last Data Sheet (no version number, Preliminary):</li> <li>Moved specifications into standard Graphic OLED template.</li> <li>In Physical Characteristics (Pg. 8) (previously "General Specifications"):</li> <li>Made distinction between overall height dimension with "FFC folded" and "FFC unfolded". Module height has not changed.</li> <li>Made distinction between "Nominal Depth" and "Maximum Depth". Module depth has not changed.</li> <li>Added specifications for "Diagonal", "FPC Bend Radius", "Module Connector Pitch", and "Weight".</li> <li>In Absolute Maximum Ratings (Pg. 16), added Humidity specification.</li> <li>Expanded "Precautions in use of OLED Modules" with important information on design and cleaning. See <u>CARE AND HANDLING PRECAUTIONS (Pg. 22)</u>.</li> <li>In Details of Interface Pin Function (Pg. 17), used Crystalfontz standard terms for signals and improved descriptions.</li> <li>In illustrations:</li> <li>Improved Module Outline Drawings (Pg. 9).</li> <li>Improved System Block Diagram (Pg. 12).</li> <li>Added circuit example using Micrel MIC2290 for V<sub>PANEL</sub> (see <u>Circuit Example – VPANEL Externally Supplied for Display (Pg. 13)</u>.</li> <li>Added circuit example <u>Connection Diagram (Pg. 14)</u>.</li> <li>Added photo with pins labeled (see <u>Photo Reference for Pin Functions (Pg. 19)</u>).</li> <li>Added definition of Viewing Angle in <u>Optical Characteristics (Pg. 20</u>).</li> </ul> |  |  |

| Continued on next | paye.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DATA SHEET                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

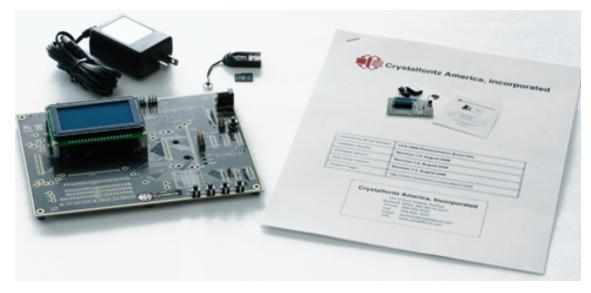

| 2010/04/09<br>Continued<br>from the<br>previous<br>page | <ul> <li>New sections, include:         <ul> <li>MAIN FEATURES (Pg. 6)</li> <li>ESD (Electro-Static Discharge) (Pg. 19).</li> <li>Sources for Sample Code (Pg. 21).</li> <li>Module Reliability (Pg. 21).</li> <li>APPENDIX A: QUALITY ASSURANCE.<br/>STANDARDS (Pg. 24).</li> <li>APPENDIX B: OLED MODULE TERMS AND<br/>SYMBOLS (Pg. 27)</li> <li>APPENDIX C: STMICROELECTRONICS STV8105<br/>CONTROLLER DATASHEET (Pg. 32)</li> </ul> </li> <li>Deleted information that is repeated in the appended<br/>controller specifications.</li> <li>This module can be ordered as part of a CFA-10009<br/>demonstration board kit. The CFA-10009 User Guide was<br/>added at the end of this Data Sheet.</li> </ul> |  |  |  |

| 2009/04/07                                              | Data Sheet version: No version number (unmarked Preliminary)<br>New Data Sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

#### The Fine Print

Certain applications using Crystalfontz America, Inc. products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications"). CRYSTALFONTZ AMERICA, INC. PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. Inclusion of Crystalfontz America, Inc. products in such applications is understood to be fully at the risk of the customer. In order to minimize risks associated with customer applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazard. Please contact us if you have any questions concerning potential risk applications.

Crystalfontz America, Inc. assumes no liability for applications assistance, customer product design, software performance, or infringements of patents or services described herein. Nor does Crystalfontz America, Inc. warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of Crystalfontz America, Inc. covering or relating to any combination, machine, or process in which our products or services might be or are used.

The information in this publication is deemed accurate but is not guaranteed.

Company and product names mentioned in this publication are trademarks or registered trademarks of their respective owners.

Copyright © 2010 by Crystalfontz America, Inc., 12412 East Saltese Avenue, Spokane Valley, WA 99216-0357 U.S.A.

## CONTENTS

| MAIN FEATURES                                                        |      |

|----------------------------------------------------------------------|------|

| Demonstration and Evaluation Platform                                | 6    |

| Comparison to LCD (Liquid Crystal Display) Module                    | 6    |

| Features                                                             | 6    |

| Module Classification Information                                    |      |

| MECHANICAL SPECIFICATIONS                                            |      |

| Physical Characteristics                                             |      |

| Module Outline Drawings                                              |      |

| ELECTRICAL SPECIFICATIONS                                            |      |

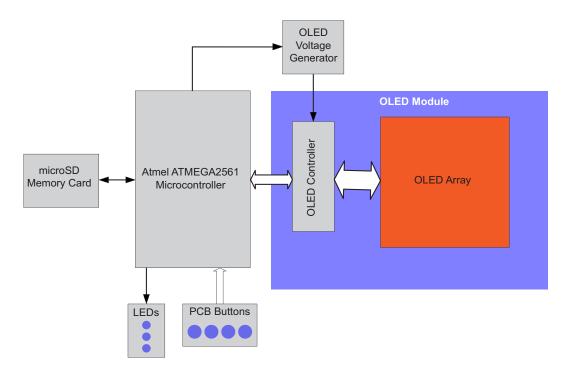

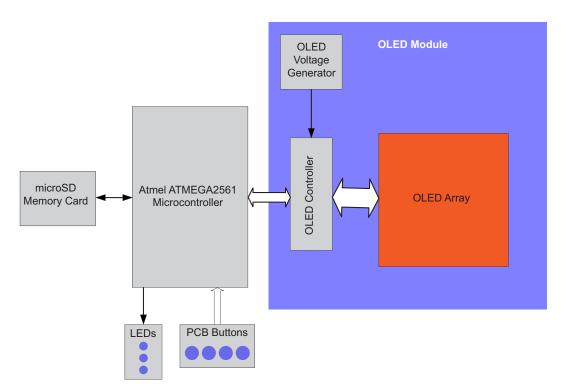

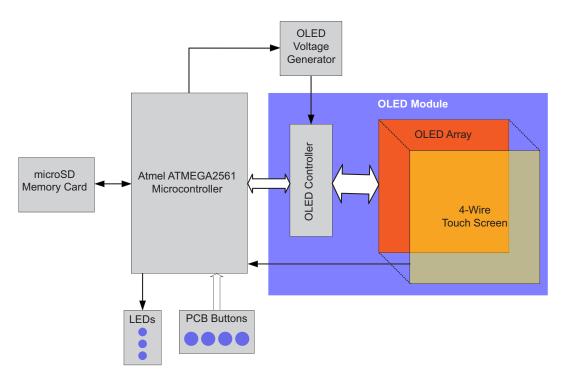

| System Block Diagram                                                 |      |

| Circuit Example – V <sub>PANEL</sub> Externally Supplied for Display | - 13 |

| Connection Diagram                                                   |      |

| Power Up and Power Down Sequencing                                   | - 15 |

| Absolute Maximum Ratings                                             |      |

| DC Characteristics                                                   |      |

| Details of Interface Pin Function                                    |      |

| Photo Reference for Pin Functions                                    |      |

| ESD (Electro-Static Discharge)                                       |      |

| OPTICAL SPECIFICATIONS                                               |      |

| Optical Characteristics                                              |      |

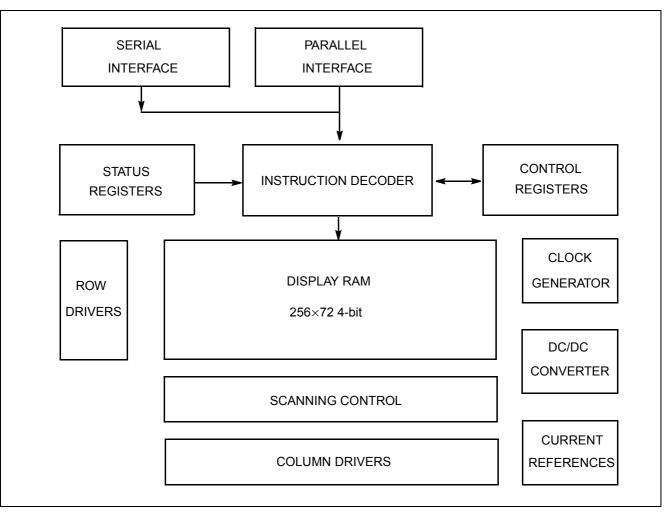

| OLED CONTROLLER INTERFACE                                            | -    |

| SAMPLE CODE                                                          |      |

| Sources For Driver Libraries                                         |      |

| Sample Code                                                          |      |

| MODULE RELIABILITY AND LONGEVITY                                     |      |

| Module Reliability                                                   |      |

| Module Longevity (EOL/Replacement Policy)                            |      |

| CARE AND HANDLING PRECAUTIONS                                        |      |

| ESD (Electro-Static Discharge)                                       |      |

| Design and Mounting                                                  |      |

| Avoid Shock, Impact, Torque, or Tension                              |      |

| Cleaning                                                             |      |

| Operation                                                            |      |

| Storage and Recycling                                                |      |

| APPENDIX A: QUALITY ASSURANCE STANDARDS                              |      |

| APPENDIX B: OLED MODULE TERMS AND SYMBOLS                            |      |

| APPENDIX C: STMICROELECTRONICS STV8105 CONTROLLER DATASHEET          | 32   |

## **LIST OF FIGURES**

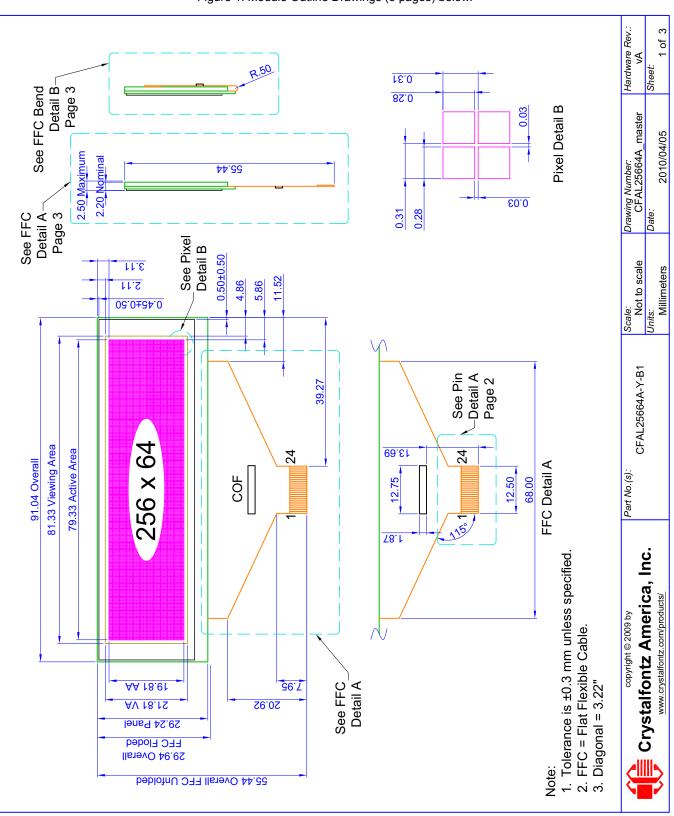

| Figure 1. | Module Outline Drawings (3 pages) below       | 9  |

|-----------|-----------------------------------------------|----|

| Figure 2. | System Block Diagram                          | 12 |

| Figure 3. | Circuit Example – External Supply for Display | 13 |

| Figure 4. | Connection Diagram                            | 14 |

| Figure 5. | Power Up and Power Down Sequencing            | 15 |

| Figure 6. | Photo Reference for Pin Functions             | 19 |

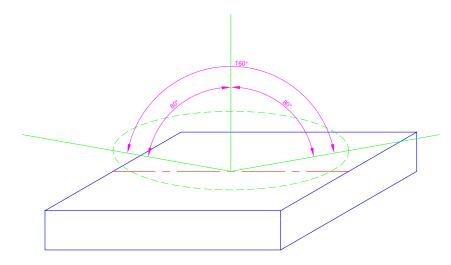

| Figure 7. | CFAL25664A-Y-B1 has a 160° Viewing Angle      | 20 |

# MAIN FEATURES

#### **DEMONSTRATION AND EVALUATION PLATFORM**

This module is available installed on a Crystalfontz CFA-10009 Demonstration PCB. The <u>DMO-L25664AYB1</u> kit has everything you need to easily demonstrate and experiment with the module. The kit can also be used as a reference for your designs. The *CFA-10009 User Guide* can be found at the end of this Data Sheet.

#### COMPARISON TO LCD (LIQUID CRYSTAL DISPLAY) MODULE

The CFAL25664A-Y-B1 is a monochrome 256 x 64 dot matrix Organic Light-Emitting Diode (OLED) display module. The small size, and ultrathin form factor of the CFAL25664A-Y-B1 makes it possible to use this OLED module in applications where it would be difficult or impossible to fit a traditional monochrome LCD module. Because of the low power requirements, the CFAL25664A-Y-B1 is suitable in battery powered portable devices such as remote controls and scientific meters (for example, temperature, sound, and gas detection).

Compared to most LCD modules, this OLED module has a quicker response time and an extremely wide viewing angle. At the low end of an STN LCD's temperature range, a module's contrast will typically be poor and the response time will be very slow. Unlike an STN LCD module, contrast does not diminish and response time is good at the lower end of an OLED module's operating temperature range, allowing it to operate in cold environments without a heater.

#### **FEATURES**

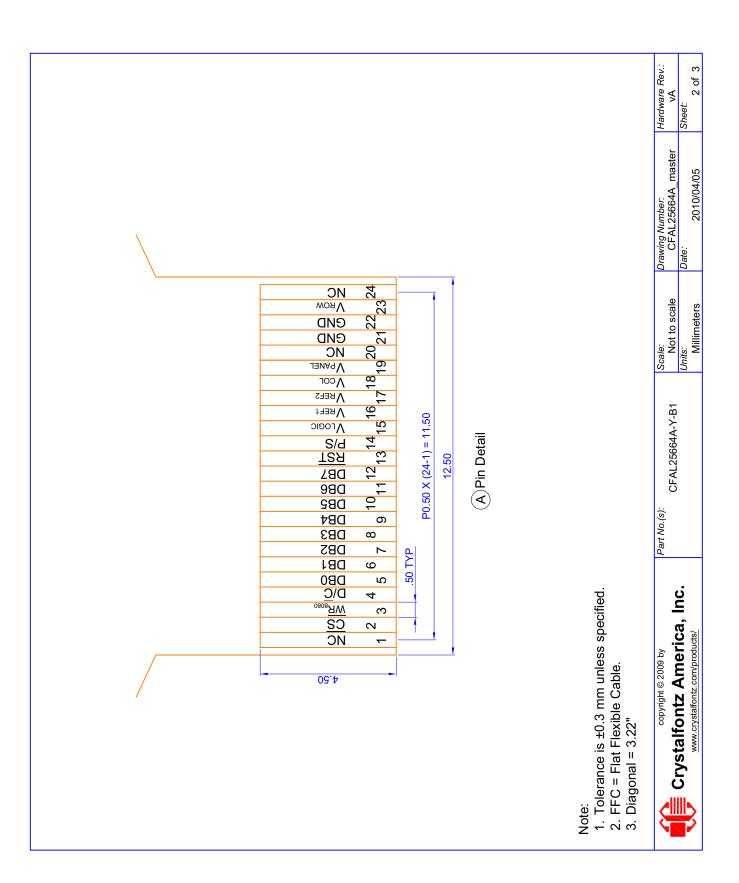

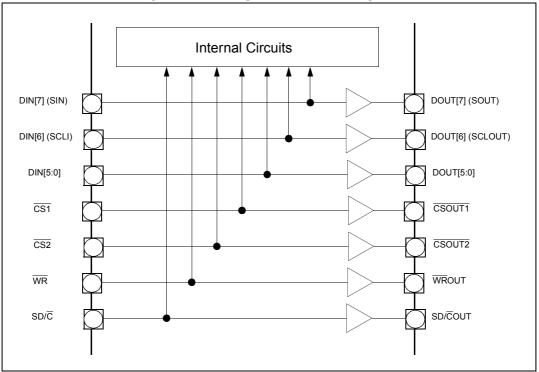

- 256 x 64 module consists of an OLED panel, a COF (Chip On Flex) driver IC, and an FFC (Flat Flexible Cable) that mates with a ZIF connector.

- □ The FFC (Flat Flex Cable) mates with standard ZIF connectors such as <u>609-1244-1-ND</u> or <u>609-1882-1-ND</u> available from Digi-Key.

- Module Dimensions

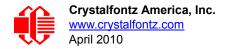

- Active Area is 3.22" diagonal, 79.33 (W) x 19.81 (H) mm (3.12" (W) x 0.78" (H)).

- Overall module dimension with FPC unfolded is 91.04 (W) x 55.44 (H) x 2.50 maximum (D) millimeters (3.58" (W) x 2.18" (H) x 0.10" maximum (D)).

- Overall module dimension with FPC *folded* is 91.04 (W) x 29.94 (H) x 2.50 maximum (D) millimeters (3.58" (W) x 1.18" (H) x 0.10" maximum (D)).

- □ Requires 3v for logic and a separate supply for V<sub>PANEL</sub>.

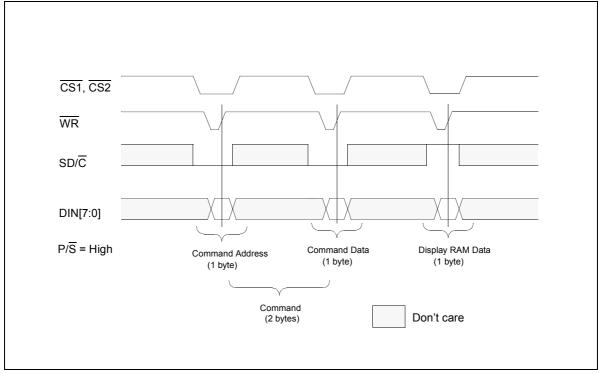

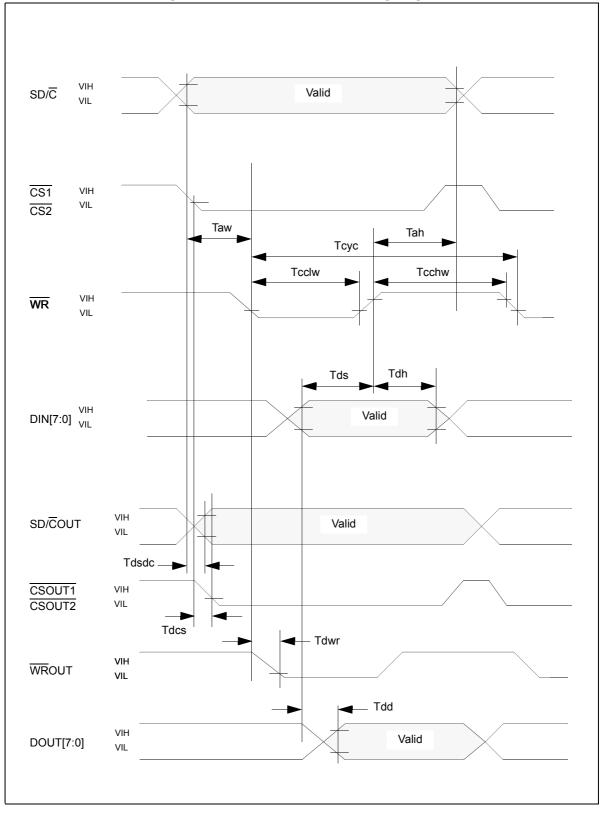

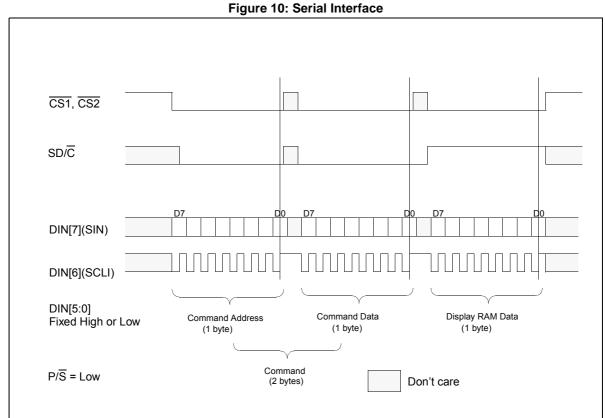

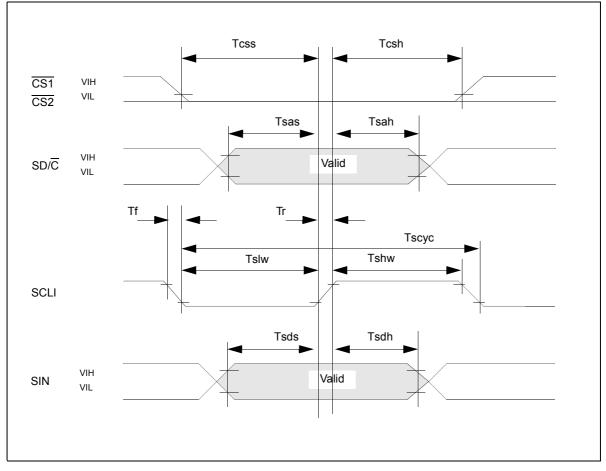

- □ 8-bit parallel (8080) interface or 4-wire Serial Peripheral Interface (SPI).

- □ <u>STMicroelectronics STV8105</u> or compatible controller.

- □ 16-level grayscale allows anti-aliased fonts.

- Emissive monochrome display. Display yellow pixels on dark area or dark pixels on yellow area (if operating with display pixels reversed/inverted).

- □ Very high contrast ratio.

- $\Box$  Extremely wide viewing angle is >160°.

- □ Wide temperature range for operation is -20°C to +70°C.

- □ RoHS compliant.

#### **MODULE CLASSIFICATION INFORMATION**

| CFA | L | <u>256</u> | <u>64</u> | Α | - | Y | - | <u>B1</u> |

|-----|---|------------|-----------|---|---|---|---|-----------|

| 0   | 2 | 3          | 4         | 6 |   | 6 |   | 7         |

| 0 | Brand                     | Crystalfontz America, Inc. |

|---|---------------------------|----------------------------|

| 0 | Display Type              | L – OLED                   |

| 0 | Number of Pixels (Width)  | 256 pixels                 |

| 4 | Number of Pixels (Height) | 64 pixels                  |

| 6 | Model Identifier          | A                          |

| 6 | Display Color             | Y – Yellow                 |

| 1 | Special Code              | B1 – Manufacturer's code   |

# **MECHANICAL SPECIFICATIONS**

#### **PHYSICAL CHARACTERISTICS**

| Number of Pixels                 |         |         |  |  |

|----------------------------------|---------|---------|--|--|

| 256 x 64 pixels = 16,384 pixels  |         |         |  |  |

| Pixel Detail Horizontal Vertical |         |         |  |  |

| Pixel Size                       | 0.28 mm | 0.28 mm |  |  |

| Pixel Pitch                      | 0.31 mm | 0.31 mm |  |  |

| Viewing Area |              |       |  |  |  |

|--------------|--------------|-------|--|--|--|

|              | Width Height |       |  |  |  |

| Millimeters  | 81.33        | 21.81 |  |  |  |

| Inches       | 3.20"        | 0.86" |  |  |  |

| Module Depth    |                        |  |  |  |

|-----------------|------------------------|--|--|--|

| Maximum Nominal |                        |  |  |  |

| 2.50            | 2.20                   |  |  |  |

| 0.10"           | 0.09"                  |  |  |  |

|                 | <b>Maximum</b><br>2.50 |  |  |  |

| Active Area |               |       |  |  |

|-------------|---------------|-------|--|--|

| Diagonal    | Inches: 3.22" |       |  |  |

|             | Width Height  |       |  |  |

| Millimeters | 79.33         | 19.81 |  |  |

| Inches      | 3.12"         | 0.78" |  |  |

| Module Overall with FFC Unfolded |       |       |  |  |  |

|----------------------------------|-------|-------|--|--|--|

| Width Height                     |       |       |  |  |  |

| Millimeters                      | 91.04 | 55.44 |  |  |  |

| Inches                           | 3.58" | 2.18" |  |  |  |

| Module Overall with FFC Folded |       |       |  |  |  |

|--------------------------------|-------|-------|--|--|--|

| Width Height                   |       |       |  |  |  |

| Millimeters                    | 91.04 | 29.94 |  |  |  |

| Inches                         | 3.58" | 1.18" |  |  |  |

| General                                                                                               |                    |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| Module Connector Pitch*                                                                               | 0.50 mm            |  |  |  |  |

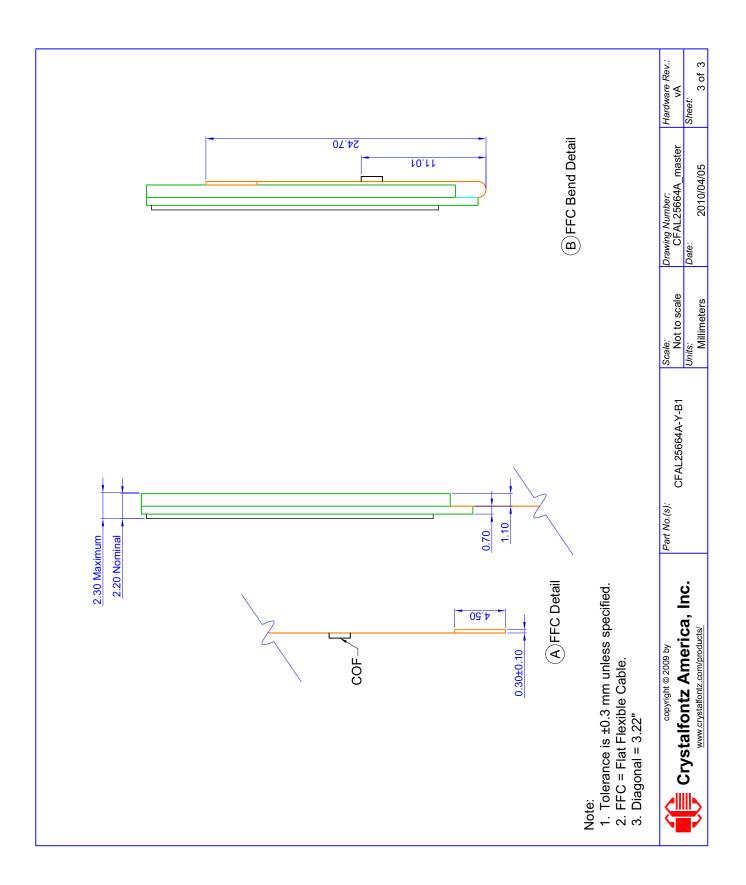

| FFC Bend Radius                                                                                       | >R5.00 mm          |  |  |  |  |

| Weight                                                                                                | 15 grams (typical) |  |  |  |  |

| *The module's 24-pin FFC mates with standa<br><u>1875-1-ND</u> and <u>609-1876-1-ND</u> available fro |                    |  |  |  |  |

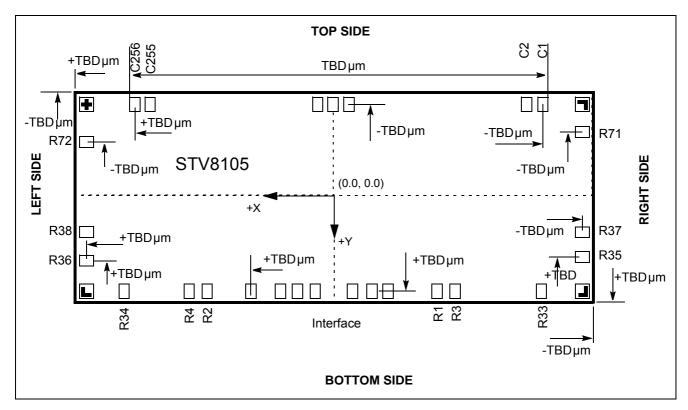

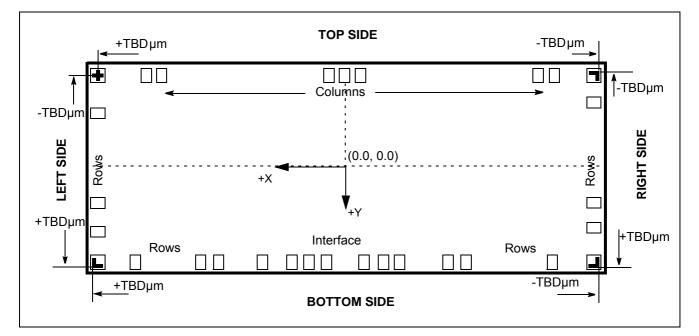

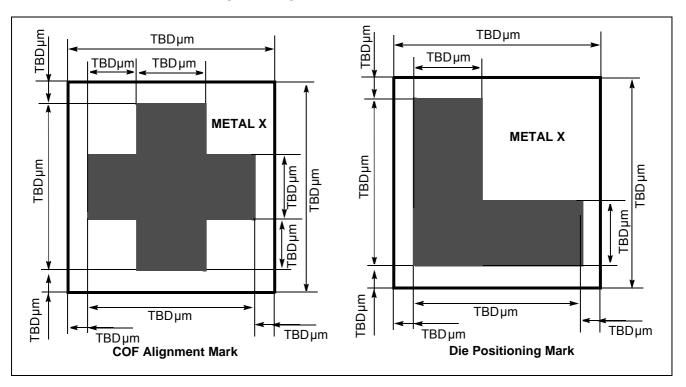

#### MODULE OUTLINE DRAWINGS

Figure 1. Module Outline Drawings (3 pages) below.

## **ELECTRICAL SPECIFICATIONS**

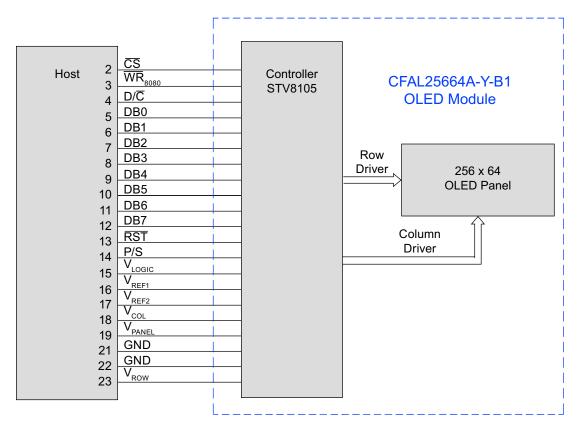

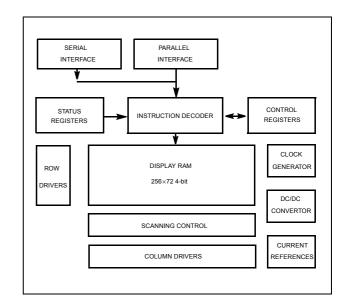

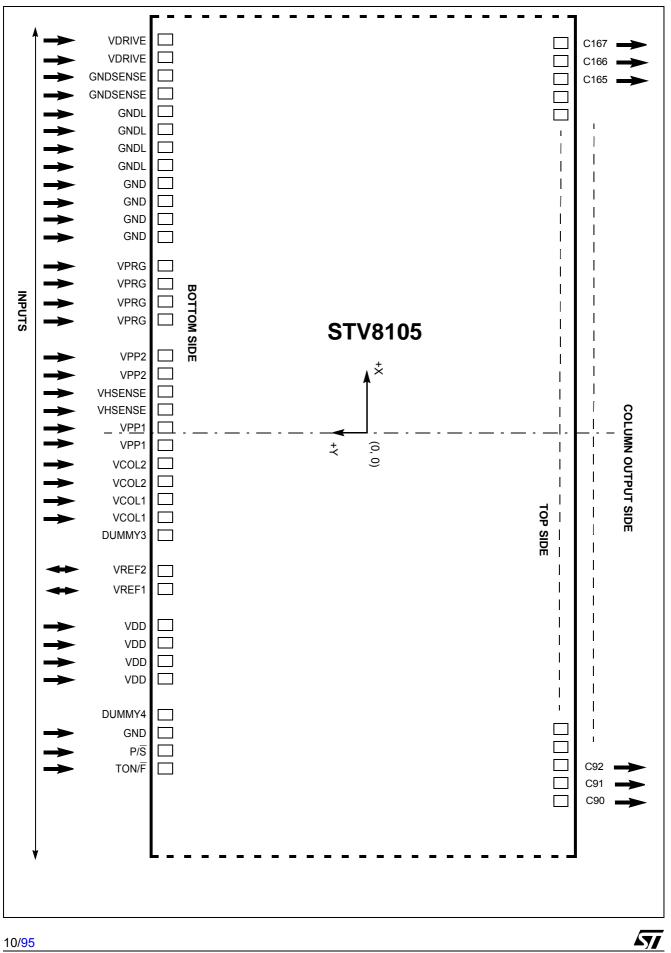

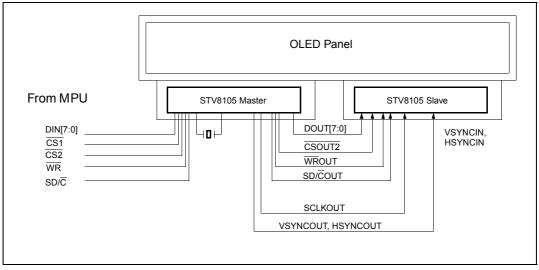

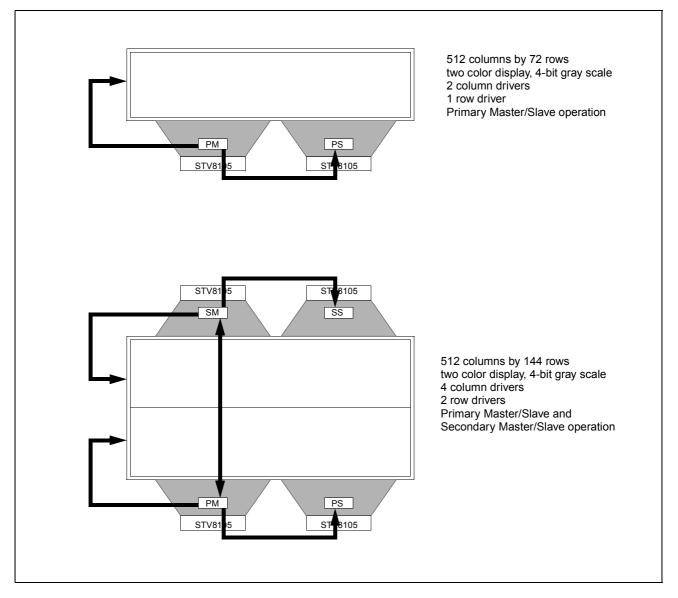

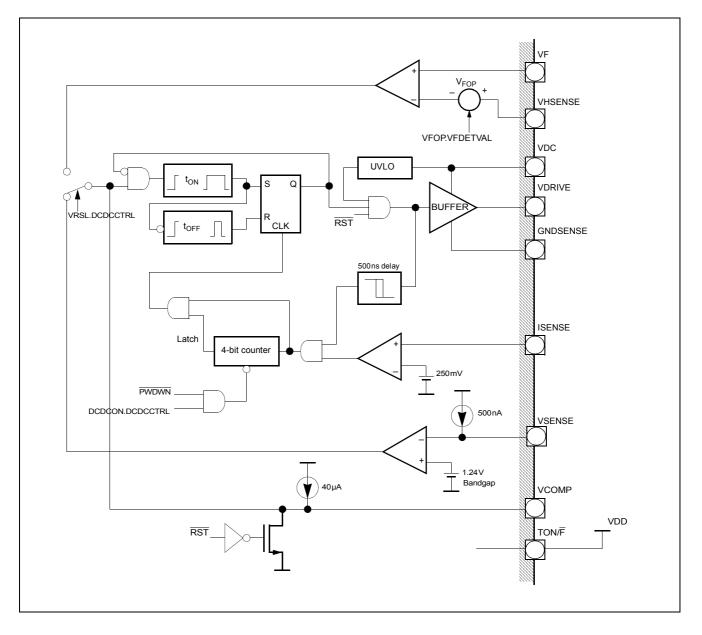

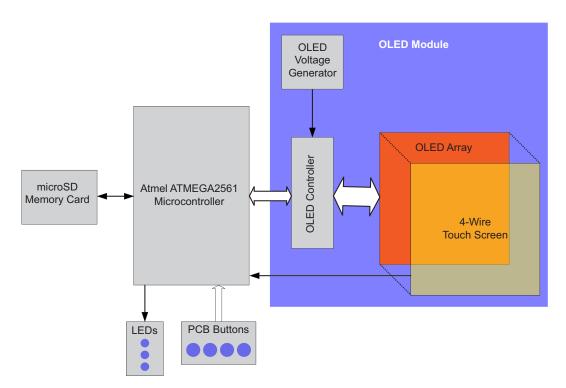

## SYSTEM BLOCK DIAGRAM

Figure 2. System Block Diagram

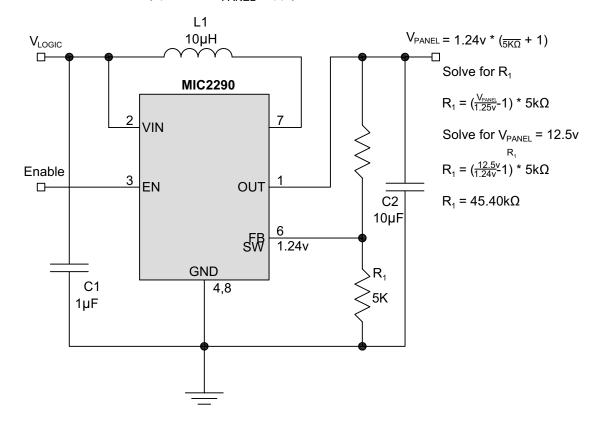

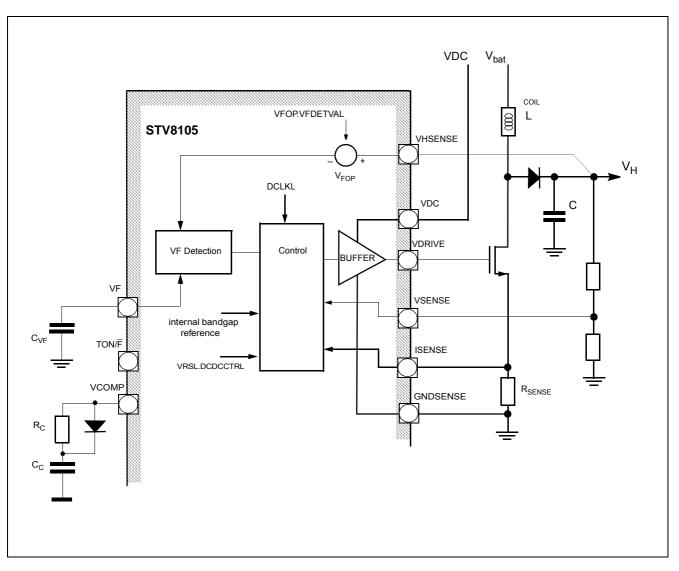

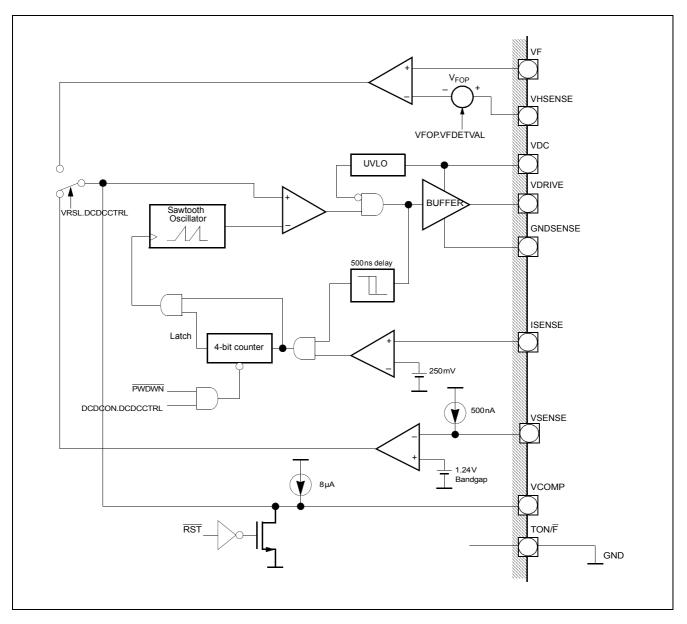

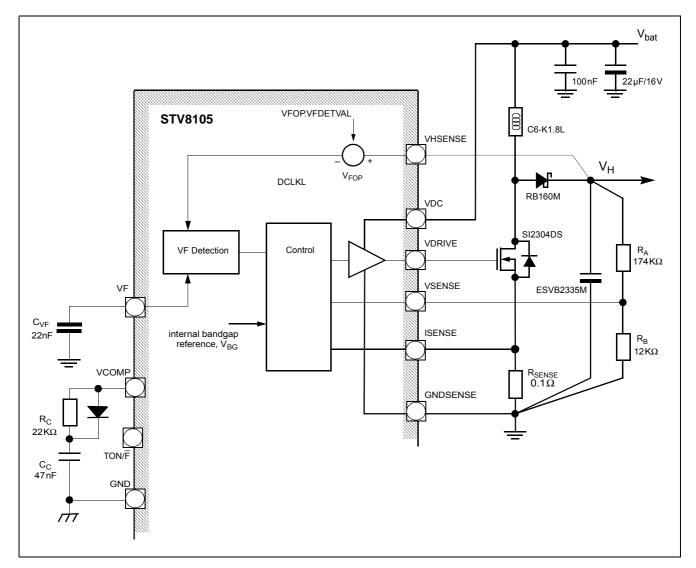

## CIRCUIT EXAMPLE – V<sub>PANEL</sub> EXTERNALLY SUPPLIED FOR DISPLAY

The Micrel MIC2290 is one of many possible V<sub>PANEL</sub> supply solutions.

Figure 3. Circuit Example – External Supply for Display

Please refer to the Micrel MIC2290 datasheet for design details. See <u>http://micrel.com/page.do?page=/product-info/products/mic2290.shtml</u>.

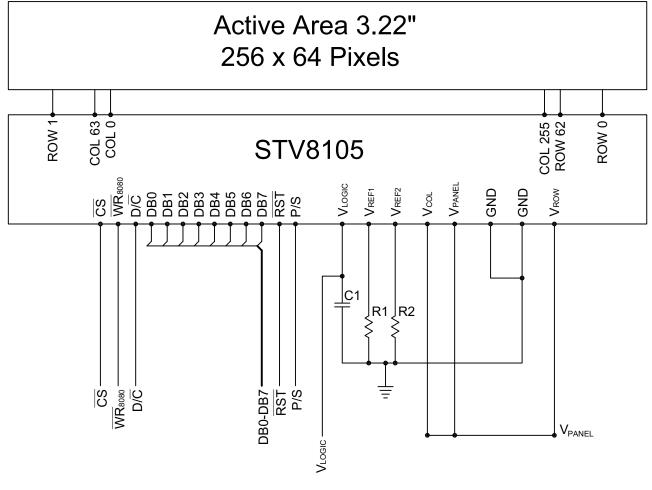

#### **CONNECTION DIAGRAM**

Figure 4. Connection Diagram

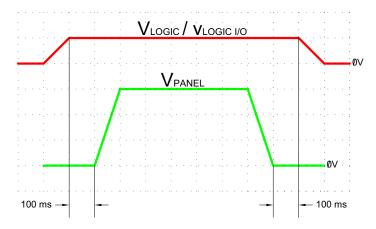

#### POWER UP AND POWER DOWN SEQUENCING

You must observe proper power sequencing for  $\mathsf{V}_{\mathsf{PANEL}}.$

*Power Up* – Display must be powered up and initialized before power is applied to V<sub>PANEL</sub>.

*Power Down* – Power must be removed from V<sub>PANEL</sub> before the display is powered off.

Figure 5. Power Up and Power Down Sequencing

#### ABSOLUTE MAXIMUM RATINGS

| ABSOLUTE MAXIMUM RATINGS                                                                                                               | SYMBOL             | WININIW | MAXIMUM |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|---------|--|--|--|--|

| Operating Temperature*                                                                                                                 | T <sub>OP</sub>    | -20°C   | +70°C   |  |  |  |  |

| Storage Temperature*                                                                                                                   | T <sub>ST</sub>    | -30°C   | +80°C   |  |  |  |  |

| Humidity                                                                                                                               | RH                 | 0%      | 90%     |  |  |  |  |

| Logic Supply Voltage                                                                                                                   | V <sub>LOGIC</sub> | +2.4v   | +3.5v   |  |  |  |  |

| Driver Supply Voltage                                                                                                                  | V <sub>PANEL</sub> | 0v      | +16.5v  |  |  |  |  |

| *Prolonged exposure at temperatures outside of this range<br>may cause permanent damage to the module or decrease<br>product lifetime. |                    |         |         |  |  |  |  |

#### **DC CHARACTERISTICS**

| DC<br>CHARACTERISTICS                      | TEST<br>CONDITION                | SYMBOL             | WINIW                                                                                                    | TYPICAL | MAXIMUM                                                                                                  |

|--------------------------------------------|----------------------------------|--------------------|----------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------|

| Logic Supply Voltage                       | $T_{OP}$ = -20°C to +70°C        | V <sub>LOGIC</sub> | +3.0v                                                                                                    | +3.3v   | +3.5v <sup>1</sup>                                                                                       |

| OLED Driver Supply<br>Voltage <sup>2</sup> | T <sub>OP</sub> = -20°C to +70°C | V <sub>PANEL</sub> |                                                                                                          | +14v    | +16.5v                                                                                                   |

| Input High Voltage                         |                                  | V <sub>IH</sub>    | +0.8v x V <sub>LOGIC</sub><br>For V <sub>LOGIC</sub> = +3.3v<br>V <sub>IH</sub> = +0.8v x +3.3v = +2.64v |         | V <sub>LOGIC</sub>                                                                                       |

| Input Low Voltage                          |                                  | V <sub>IL</sub>    | 0v (GND)                                                                                                 |         | +0.2v x V <sub>LOGIC</sub><br>For V <sub>LOGIC</sub> = +3.3v<br>V <sub>IL</sub> = +0.2v x +3.3v = +0.66v |

| Output High Voltage                        | I <sub>OUT</sub> = <1 mA         | V <sub>OH</sub>    | +0.8v x V <sub>LOGIC</sub><br>For V <sub>LOGIC</sub> = +3.3v<br>V <sub>IH</sub> = +0.8v x +3.3v = +2.64v |         | V <sub>LOGIC</sub>                                                                                       |

| Output Low Voltage                         | I <sub>OUT</sub> = <1 mA         | V <sub>OL</sub>    | 0v (GND)                                                                                                 |         | +0.2v x V <sub>LOGIC</sub><br>For V <sub>LOGIC</sub> = +3.3v<br>V <sub>IL</sub> = +0.2v x +3.3v = +0.66v |

<sup>1</sup>Do not exceed +3.5v maximum.

$^{2}$ The V<sub>PANEL</sub> input must be a stable value with no ripple or noise.

This is a summary of the module's major operating parameters. For detailed information see <u>APPENDIX C: STMICROELECTRON-ICS STV8105 CONTROLLER DATASHEET (Pg. 32)</u>

Г

-

## DETAILS OF INTERFACE PIN FUNCTION

| PIN | SIGNAL             | LEVEL | DIRECTION | DESCRIPTION                                                                                                                                                                                            |  |

|-----|--------------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | NC                 |       |           | Make no connection.                                                                                                                                                                                    |  |

|     |                    |       |           | Chip select input.                                                                                                                                                                                     |  |

| 2   | CS                 | H/L   | I         | <i>Low:</i> Controller chip is selected. Communications with the host is possible.                                                                                                                     |  |

|     |                    |       |           | <i>High:</i> Controller chip is not selected. Host interface signals are ignored by the controller.                                                                                                    |  |

|     |                    |       |           | Host interface input.                                                                                                                                                                                  |  |

| 3   | WR <sub>8080</sub> | H/L   | I         | 8080 Host: Active low. Signal on the databus is latched at the rising edge of $\overline{\text{WR}}$ signal.                                                                                           |  |

|     |                    |       |           | SPI (serial) mode: Connect to ground.                                                                                                                                                                  |  |

|     | _                  |       |           | Data/Command control. Determines whether data bits are data or command.                                                                                                                                |  |

| 4   | D/C                | H/L   | I         | 1 – High: Addresses the data register.                                                                                                                                                                 |  |

|     |                    |       |           | 2 – Low: Addresses the command register.                                                                                                                                                               |  |

| 5   | DB0                | H/L   | I/O       |                                                                                                                                                                                                        |  |

| 6   | DB1                | H/L   | I/O       | Bidirectional databus connects to 8-bit standard host databus.                                                                                                                                         |  |

| 7   | DB2                | H/L   | I/O       | <i>In SPI (serial) mode (IS1=0, IS2=0):</i> DB6 serves as the serial clock input signal (SCL) and DB7 serves as the serial data input pin (SI).                                                        |  |

| 8   | DB3                | H/L   | I/O       | DB2-DB7 are high impedance. In serial mode, data can be written to                                                                                                                                     |  |

| 9   | DB4                | H/L   | I/O       | the display but not read. Pin 3 (WR <sub>8080</sub> ) is unused and should be tied low.                                                                                                                |  |

| 10  | DB5                | H/L   | I/O       |                                                                                                                                                                                                        |  |

| 11  | DB6                | H/L   | I/O       | <i>In 8080 Parallel mode:</i> Pin 3 is used as WR <sub>8080.</sub> Data is input or output on DB0-DB7.                                                                                                 |  |

| 12  | DB7                | H/L   | I/O       |                                                                                                                                                                                                        |  |

| 13  | RST                | H/L   | Ι         | Reset signal.<br><i>Low:</i> Display controller is reset. The RST pin should be pulsed low<br>shortly after power is applied.<br><i>High:</i> The RST pin should be brought high for normal operation. |  |

| PIN       | SIGNAL             | LEVEL                | DIRECTION | DESCRIPTION (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----------|--------------------|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 14        | P/S                | H/L                  | I         | P/SInterface Mode0SPI (Serial)18080 Parallel                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 15        | V <sub>LOGIC</sub> | +3.0v<br>to<br>+3.3v | I         | Power supply input. Must be connected to an external source.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

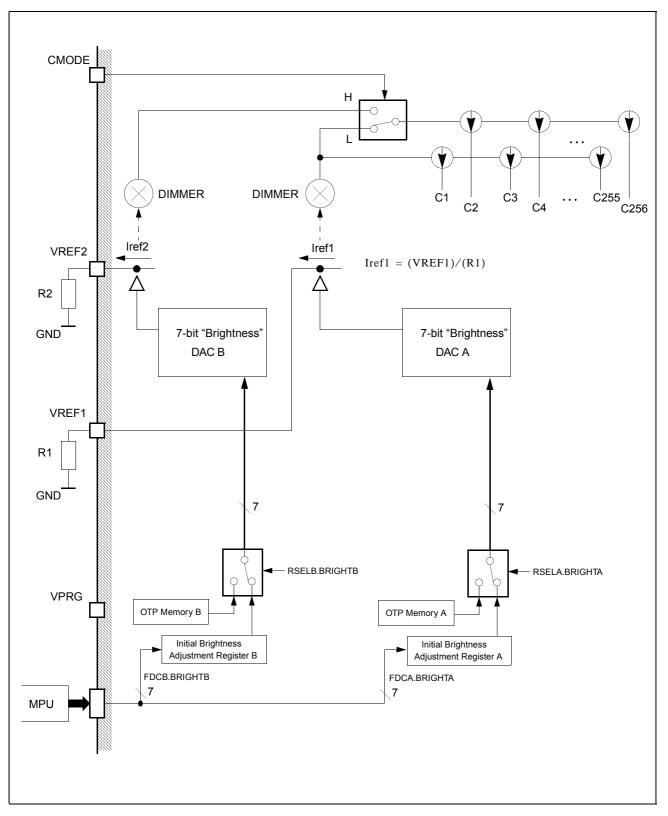

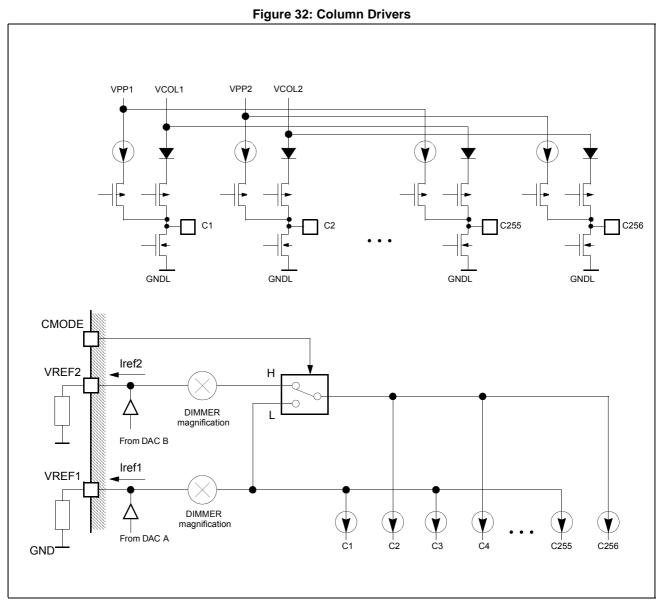

| 16        | V <sub>REF1</sub>  | Ю                    |           | Reference Voltage. A 6.8k resistor should be connected to the pin to GND. See <u>APPENDIX C: STMICROELECTRONICS STV8105</u><br><u>CONTROLLER DATASHEET (Pg. 32)</u> for more information.                                                                                                                                                                                                                                                       |  |  |

| 17        | V <sub>REF2</sub>  | IO                   |           | Reference Voltage. A 6.8k resistor should be connected to the pin to GND. See <u>APPENDIX C: STMICROELECTRONICS STV8105</u><br><u>CONTROLLER DATASHEET (Pg. 32)</u> for more information.                                                                                                                                                                                                                                                       |  |  |

| 18        | V <sub>COL</sub>   | IO                   |           | Column Supply Voltage. This is odd and even column supply voltage. It can be supplied externally or by connecting to V <sub>PANEL</sub> .                                                                                                                                                                                                                                                                                                       |  |  |

| 19        | V <sub>PANEL</sub> | +14v                 | I         | <ul> <li>Driver supply voltage. Only high voltage input on chip. Power must be supplied externally.</li> <li>Note: You must observe power sequencing for this signal. See <u>Power</u> <u>Up and Power Down Sequencing (Pg. 15)</u>.</li> <li>Power Up – Display must be powered up and initialized before power is applied to the pin.</li> <li>Power Down – Power must be removed from this pin before the display is powered off.</li> </ul> |  |  |

| 20        | NC                 |                      |           | Make no connection.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 21-<br>22 | GND                | 0v                   |           | Power supply and signal ground. Must be connected to an external ground.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 23        | V <sub>ROW</sub>   |                      |           | Row Driver Supply. This is odd and even row power supply. It can be supplied externally or by connecting to $V_{\mbox{PANEL}}.$                                                                                                                                                                                                                                                                                                                 |  |  |

| 24        | NC                 |                      |           | Make no connection.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

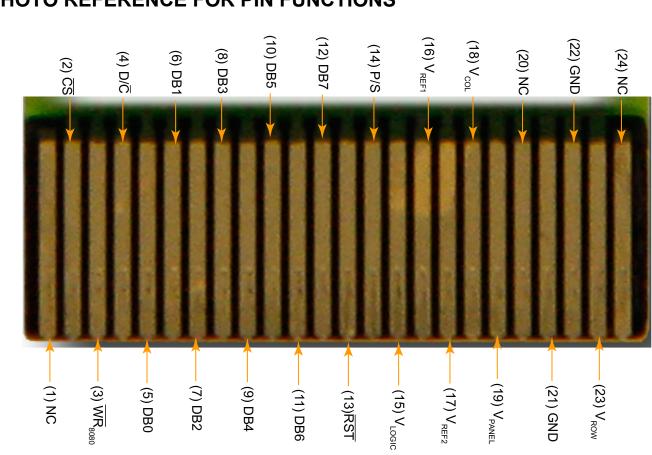

#### PHOTO REFERENCE FOR PIN FUNCTIONS

Figure 6. Photo Reference for Pin Functions

#### **ESD (ELECTRO-STATIC DISCHARGE)**

The circuitry is industry standard CMOS logic and susceptible to ESD damage. Please use industry standard antistatic precautions as you would for any other static sensitive devices such as expansion cards, motherboards, or integrated circuits. Ground your body, work surfaces, and equipment.

# **OPTICAL SPECIFICATIONS**

#### **OPTICAL CHARACTERISTICS**

| ITEM                                                                                                                                                                                                            | SYMBOL          | TEST CONDITION       | WIWINIW | TYPICAL              | MAXIMUM |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------|----------------------|---------|--|--|

| Viewing Angle                                                                                                                                                                                                   |                 |                      |         | <u>&gt;</u> 160°     |         |  |  |

| Dark Room Contrast Ratio <sup>1</sup>                                                                                                                                                                           | CR              | 80 cd/m <sup>2</sup> |         | <u>&gt;</u> 100:1    |         |  |  |

| Luminous Intensity                                                                                                                                                                                              | L <sub>BR</sub> |                      |         | 80 cd/m <sup>2</sup> |         |  |  |

| Duty                                                                                                                                                                                                            | 1/64            |                      |         |                      |         |  |  |

| <sup>1</sup> Contrast Ratio = (brightness with pixels light)/(brightness with pixels dark).<br><sup>2</sup> Response Time: The amount of time it takes a pixel to change from active to inactive or back again. |                 |                      |         |                      |         |  |  |

#### **Definition of Viewing Angle**

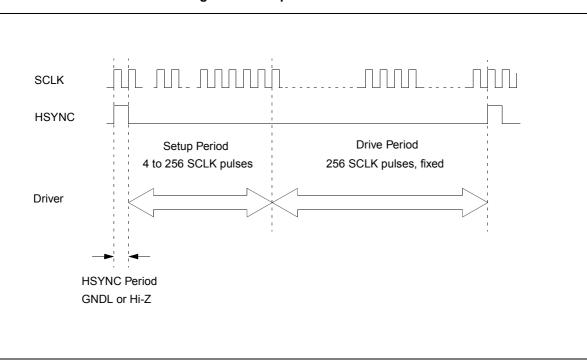

## OLED CONTROLLER INTERFACE

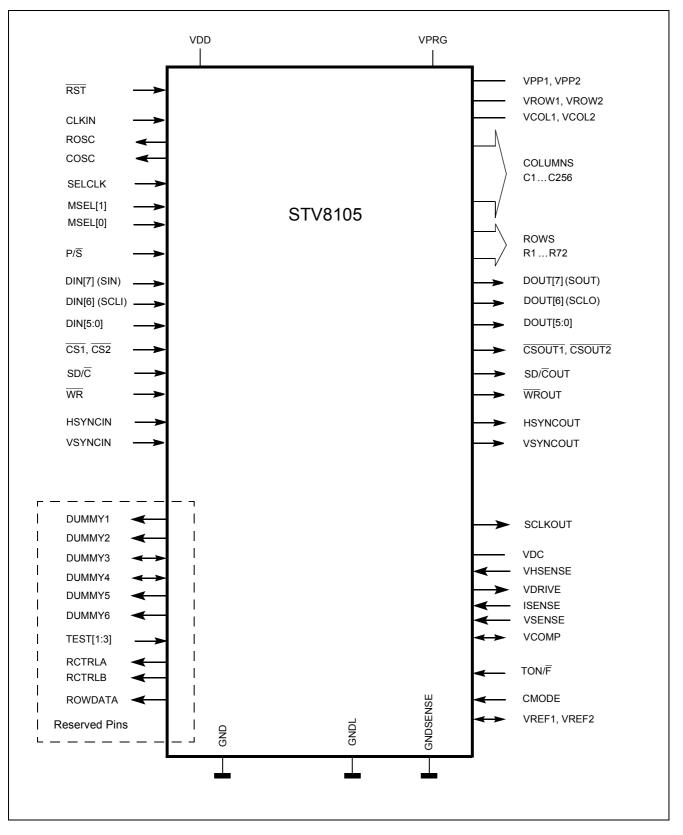

This module uses a STMicroelectronics STV8105 controller. For your reference, we added <u>APPENDIX C:</u> <u>STMICROELECTRONICS STV8105 CONTROLLER DATASHEET (Pg. 32)</u> to this Data Sheet.

## SAMPLE CODE

## SOURCES FOR DRIVER LIBRARIES

Graphic driver libraries may save a lot of time and help you develop a more professional product. Possible library sources are <u>easyGUI</u>, <u>en.radzio.dxp.pl</u>, <u>Gwentech</u>, <u>Micriµm</u>, <u>RAMTEX</u>, and <u>Segger emWin</u>.

#### SAMPLE CODE

You can download our sample code from here: http://www.crystalfontz.com/products/document/2088/CFAL25664A.zip.

Note: Please observe V<sub>PANEL</sub> sequencing as described in <u>Details of Interface Pin Function (Pg. 17)</u>. See also <u>Power Up</u> and <u>Power Down Sequencing (Pg. 15)</u>.

## MODULE RELIABILITY AND LONGEVITY

#### MODULE RELIABILITY

| AVERAGE<br>BRIGHTNESS | SPECIFICATION                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------|

| 80 cd/m <sup>2</sup>  | Brightness will be >50% of a new module's initial brightness for at least 10,000 hours of operation. |

| 40 cd/m <sup>2</sup>  | 20,000 hours.                                                                                        |

| Test Condition: 2     | 25°C.                                                                                                |

OLED displays are an emissive technology. Each pixel is susceptible to dimming based on its individual use (burn-in). Frequently used pixels will dim more quickly than pixels that are not used as often. Please avoid using a bright, static, high-contrast image for a long time. If you want to leave the display powered on, please use scrolling text or alternating images to "wear level" the pixels. To conserve power and display lifetime, turn off or dim the display when it is not in use.

#### MODULE LONGEVITY (EOL/REPLACEMENT POLICY)

Crystalfontz is committed to making all of our modules available for as long as possible. For each module we introduce, we intend to offer it indefinitely. We do not preplan a module's obsolescence. The majority of modules we have introduced are still available.

We recognize that discontinuing a module may cause problems for some customers. However, rapidly changing technologies, component availability, or low customer order levels may force us to discontinue ("End of Life", EOL) a module. For example, we must occasionally discontinue a module when a supplier discontinues a component or a manufacturing process becomes obsolete. When we discontinue a module, we will do our best to find an acceptable replacement module with the same fit, form, and function.

In most situations, you will not notice a difference when comparing a "fit, form, and function" replacement module to the discontinued module. However, sometimes a change in component or process for the replacement module results in a slight variation, perhaps an improvement, over the previous design.

Although the replacement module is still within the stated Data Sheet specifications and tolerances of the discontinued module, changes may require modification to your circuit and/or firmware. Possible changes include:

- Controller. A new controller may require minor changes in your code.

- *Component tolerances.* Module components have manufacturing tolerances. In extreme cases, the tolerance stack can change the visual or operating characteristics.

Please understand that we avoid changing a module whenever possible; we only discontinue a module if we have no other option. We will post Part Change Notices on the product's webpage as soon as possible. If interested, you can subscribe to future part change notifications.

## **CARE AND HANDLING PRECAUTIONS**

For optimum operation of the module and to prolong its life, please follow the precautions below. Excessive voltage will shorten the life of the module. You must drive the display within the specified voltage limit. See <u>Absolute Maximum</u> <u>Ratings (Pg. 16)</u>.

#### **ESD (ELECTRO-STATIC DISCHARGE)**

The circuitry is industry standard CMOS logic and susceptible to ESD damage. Please use industry standard antistatic precautions as you would for any other static sensitive devices such as expansion cards, motherboards, or integrated circuits. Ground your body, work surfaces, and equipment.

#### **DESIGN AND MOUNTING**

- The exposed surface of the "glass" is actually a polarizer laminated on top of the glass. To protect the soft plastic polarizer from damage, the module ships with a protective film over the polarizer. Please peel off the protective film slowly. Peeling off the protective film abruptly may generate static electricity.

- The polarizer is made out of soft plastic and is easily scratched or damaged. When handling the module, avoid touching the polarizer. Finger oils are difficult to remove.

- To protect the soft plastic polarizer from damage, place a transparent plate (for example, acrylic, polycarbonate, or glass) in front of the module, leaving a small gap between the plate and the display surface. We use GE HP-92 Lexan, which is readily available and works well.

- Do not disassemble or modify the module.

- Do not reverse polarity to the power supply connections. Reversing polarity will immediately ruin the module.

- The FFC (Flat Flex Cable) mates with standard ZIF connectors such as <u>609-1244-1-ND</u> or <u>609-1882-1-ND</u> available from Digi-Key.

- Sharp bends can damage the FFC. Do not crease FFC. Do not bend FFC tightly against the edge of the OLED panel. Limit bend radius to >R5.00 mm.

- Do not repeatedly bend the FFC beyond its elastic region.

#### AVOID SHOCK, IMPACT, TORQUE, OR TENSION

- Do not expose the module to strong mechanical shock, impact, torque, or tension.

- Do not drop, toss, bend, or twist the module.

• Do not place weight or pressure on the module.

#### CLEANING

- The polarizer (laminated to the glass) is soft plastic. The soft plastic is easily scratched or damaged. Be very careful when you clean the polarizer.

- Do not clean the polarizer with liquids. Do not wipe the polarizer with any type of cloth or swab (for example, Q-tips).

- Use the removable protective film to remove smudges (for example, fingerprints) and any foreign matter. If you no longer have the protective film, use standard transparent office tape (for example, Scotch® brand "Crystal Clear Tape"). If the polarizer is dusty, you may carefully blow it off with clean, dry, oil-free compressed air.

#### **OPERATION**

- We do not recommend connecting this module to a PC's parallel port as an "end product." This module is not "user friendly" and connecting it to a PC's parallel port is often difficult, frustrating, and can result in a "dead" display due to mishandling. For more information, see our forum thread at <a href="http://www.crystalfontz.com/forum/showthread.php?s=&threadid=3257">http://www.crystalfontz.com/forum/showthread.php?s=&threadid=3257</a>.

- Your circuit should be designed to protect the module from ESD and power supply transients.

- Observe the operating temperature limitations: from -20°C minimum to +70°C maximum with minimal fluctuations. Operation outside of these limits may shorten the life and/or harm the display.

- Operate away from dust, moisture, and direct sunlight.

# STORAGE AND RECYCLING

- Store in an ESD-approved container away from dust, moisture, and direct sunlight, fluorescent lamps, or any ultraviolet ray.

- Observe the storage temperature limitations: from -30°C minimum to +80°C maximum with minimal fluctuations. Rapid temperature changes can cause moisture to form, resulting in permanent damage.

- Do not allow weight to be placed on the modules while they are in storage.

- Please recycle your outdated Crystalfontz modules at an approved facility.

# **APPENDIX A: QUALITY ASSURANCE STANDARDS**

#### **INSPECTION CONDITIONS**

- Environment

- Temperature: 25±5°C

- Humidity: 30~85% RH (noncondensing)

- For visual inspection of active display area

- Source lighting: two 20-Watt or one 40-Watt fluorescent light

- Display adjusted for best contrast

- Viewing distance: 30±5 cm (about 12 inches)

- Viewing angle: inspect at 45° angle of vertical line right and left, top and bottom

#### **COLOR DEFINITIONS**

We try to describe the appearance of our modules as accurately as possible. For the photos, we adjust for optimal appearance. Actual display appearance may vary due to (1) different operating conditions, (2) small variations of component tolerances, (3) inaccuracies of our camera, (4) color interpretation of the photos on your monitor, and/or (5) personal differences in the perception of color.

#### **DEFINITION OF ACTIVE AREA AND VIEWING AREA**

#### ACCEPTANCE SAMPLING

| DEFECT TYPE                                         | AQL*                            |

|-----------------------------------------------------|---------------------------------|

| Major                                               | <u>&lt;</u> .65%                |

| Minor                                               | <1.0%                           |

| * Acceptable Quality Level: maximum allowable error | rate or variation from standard |

## DEFECTS CLASSIFICATION

Defects are defined as:

- Major Defect: results in failure or substantially reduces usability of unit for its intended purpose.

- Minor Defect: deviates from standards but is not likely to reduce usability for its intended purpose.

#### **ACCEPTANCE STANDARDS**

| # | DEFECT TYPE                                             |                       | CRITERIA                                                                                                                        |                | MAJOR /<br>MINOR |  |  |

|---|---------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--|--|

| 1 | Electrical defects                                      |                       | <ol> <li>No display, display malfunctions, or shorted segments.</li> <li>Current consumption exceeds specifications.</li> </ol> |                |                  |  |  |

| 2 | Viewing area defect                                     | Viewing area does not | meet specifications.                                                                                                            |                | Major            |  |  |

| 3 | 3 Blemishes or foreign<br>matter on display<br>segments | Blemish               | Defect Size                                                                                                                     | Acceptable Qty |                  |  |  |

|   |                                                         |                       | <u>&lt;</u> 0.30 mm                                                                                                             | 3              | Minor            |  |  |

|   |                                                         |                       | $\leq$ 2 defects within 10 mm of each other                                                                                     |                | Minor            |  |  |

| 4 | Dark lines or scratches                                 | Defect Width          | Defect Length                                                                                                                   | Acceptable Qty |                  |  |  |

|   | in display area                                         | <u>&lt;</u> 0.03 mm   | <u>&lt;</u> 3.0 mm                                                                                                              | 3              |                  |  |  |

|   | ×                                                       | 0.03 to 0.05          | <u>&lt;</u> 2.0 mm                                                                                                              | 2              | Minor            |  |  |

|   | Length                                                  | 0.05 to 0.08          | <u>&lt;</u> 2.0 mm                                                                                                              | 1              | WILLOI           |  |  |

|   |                                                         | 0.08 to 0.10          | ≤3.0 mm                                                                                                                         | 0              |                  |  |  |

|   |                                                         | <u>&gt;</u> 0.10      | >3.0 mm                                                                                                                         | 0              |                  |  |  |

#### ACCEPTANCE STANDARDS

| # | DEFECT TYPE              |                                                                                                                                                                                                                                                                                                                                           | CRITERIA                                                                                                                                                                                                                                                                                                                  |                | MAJOR /<br>MINOR |  |

|---|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--|

| 5 | Bubbles between polarize | r film and glass                                                                                                                                                                                                                                                                                                                          | Defect Size                                                                                                                                                                                                                                                                                                               | Acceptable Qty |                  |  |

|   |                          |                                                                                                                                                                                                                                                                                                                                           | <u>&lt;</u> 0.20 mm                                                                                                                                                                                                                                                                                                       | Ignore         |                  |  |

|   |                          |                                                                                                                                                                                                                                                                                                                                           | 0.20 to 0.40 mm                                                                                                                                                                                                                                                                                                           | 3              | Minor            |  |

|   |                          |                                                                                                                                                                                                                                                                                                                                           | 0.40 to 0.60 mm                                                                                                                                                                                                                                                                                                           | 2              |                  |  |

|   |                          |                                                                                                                                                                                                                                                                                                                                           | <u>&gt;</u> 0.60 mm                                                                                                                                                                                                                                                                                                       | 0              |                  |  |

| 6 | Display pattern defect   |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                           |                | Minor            |  |

|   |                          | Pixel Size                                                                                                                                                                                                                                                                                                                                | Acce                                                                                                                                                                                                                                                                                                                      | ptable Qty     |                  |  |

|   |                          | ((A+B)/2) <u>&lt;</u> 0.20 mm                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                         |                |                  |  |

|   |                          | C>0 mm                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                         | tal defects    |                  |  |

|   |                          | ((D+E)/2) <u>&lt;</u> 0.25 mm                                                                                                                                                                                                                                                                                                             | <u>&lt;</u> 2 pinin                                                                                                                                                                                                                                                                                                       | oles per digit |                  |  |

|   |                          | ((F+G)/2) <u>&lt;</u> 0.25 mm                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                           |                |                  |  |

| 7 | PCB defects              | <ol> <li>Oxidation or contamination on connectors.*</li> <li>Wrong parts, missing parts, or parts not in specification.*</li> <li>Jumpers set incorrectly.</li> <li>Solder (if any) on bezel, LED pad, zebra pad, or screw hole pad is not smooth.</li> <li>*Minor if display functions correctly. Major if the display fails.</li> </ol> |                                                                                                                                                                                                                                                                                                                           |                |                  |  |

| 8 | Soldering defects        | <ol> <li>Cold solder joints, mi</li> <li>Solder bridges causir</li> <li>Residue or solder ba</li> <li>Solder flux is black or</li> </ol>                                                                                                                                                                                                  | <ol> <li>Unmelted solder paste.</li> <li>Cold solder joints, missing solder connections, or oxidation.*</li> <li>Solder bridges causing short circuits.*</li> <li>Residue or solder balls.</li> <li>Solder flux is black or brown.</li> <li>*Minor if display functions correctly. Major if the display fails.</li> </ol> |                |                  |  |

## **APPENDIX B: OLED MODULE TERMS AND SYMBOLS**

| Symbol                                | Description                                                                                                                                                                                                                                                                    |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| С                                     | Capacitor                                                                                                                                                                                                                                                                      |  |

| cd/m <sup>2</sup><br>nit              | Candela meter squared is the standard unit of measurement for luminous intensity (photometric brightness).                                                                                                                                                                     |  |

| CIE                                   | A color model based on human perception developed by the CIE (Commission Internationale de l'Eclairage) committee.                                                                                                                                                             |  |

| CLS                                   | Clock select pin.                                                                                                                                                                                                                                                              |  |

| COF<br>COT<br>TAB                     | Chip On Flex. Controller is on the FPC. Similar in appearance to "TAB." The flex circuit on COF is typically much thinner than the flex of a "flex tail."                                                                                                                      |  |

| COG                                   | Chip On Glass. Controller is on the glass panel.                                                                                                                                                                                                                               |  |

| СОМ                                   | Common driver. Common signal output for OLED display.                                                                                                                                                                                                                          |  |

| CR                                    | Contrast Ratio = (brightness with pixels light)/(brightness with pixels dark).                                                                                                                                                                                                 |  |

| CS<br>CS#<br>CSB                      | <ul> <li>Chip select input.</li> <li><i>Low:</i> Controller chip is selected. Communications with host is possible.</li> <li><i>High:</i> Controller chip is not selected. Host interface signals are ignored by the controller.</li> </ul>                                    |  |

| D                                     | Diode                                                                                                                                                                                                                                                                          |  |

| DB0 ~ DB <i>n</i><br>D0 ~ D <i>n</i>  | Bidirectional databus connects to 8-bit or 16-bit standard host databus. When SPI (serial interface) is selected, DB6 serves as the serial clock input signal (SCL or SCLK) and DB7 serves as the serial data input signal (SI or SDIN). DB2 to DBn are set to high impedance. |  |

| D/C<br>RS<br>A0<br>CD<br>D/C#<br>SD/C | <ul> <li>Data/Command control. Determines whether data bits are data or command.</li> <li>1 – High: Addresses the data register.</li> <li>0 – Low: Addresses the command register.</li> </ul>                                                                                  |  |

| ESD                                   | Electro-Static Discharge. Sudden and brief electrical current that flows between two objects.<br>ESD between a human and a OLED module can cause permanent damage.                                                                                                             |  |

| FB                                    | Feedback input for the booster circuit. Use to adjust booster output voltage level, $V_{PANEL}$                                                                                                                                                                                |  |

| FFC                                   | Flat Flex Cable. Used for Touch Screen connection. Also called "pigtail."                                                                                                                                                                                                      |  |

| FG                                    | Frame Ground.                                                                                                                                                                                                                                                                  |  |

| FPC                                   | Flexible Printed Circuit. Also called "flex tail." Typically much thicker than the "flex" film of COF (Chip On Flex).                                                                                                                                                          |  |

| GDR                                   | Gate Drive. Output signal drives the gate of the external NMOS of the booster circuit.                                                                                                                                                                                         |  |

| Symbol                                                | Description (Continued)                                                                                                                       |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GND<br>V <sub>SS</sub>                                | Power supply and signal ground. Must be connected to an external ground.                                                                      |  |  |

| I <sub>LOGIC</sub><br>I <sub>DD</sub>                 | Operating current for V <sub>LOGIC</sub> .                                                                                                    |  |  |

| I <sub>LOGIC</sub> , SLEEP<br>I <sub>DD</sub> , SLEEP | Sleep mode current for V <sub>LOGIC</sub> .                                                                                                   |  |  |

| I <sub>PANEL</sub><br>I <sub>CC</sub>                 | Supply current for V <sub>PANEL.</sub>                                                                                                        |  |  |

| I <sub>PANEL</sub> , SLEEP<br>I <sub>CC</sub> , SLEEP | Sleep mode current for V <sub>PANEL</sub>                                                                                                     |  |  |

| I <sub>REF</sub>                                      | Segment output current reference for brightness adjustment. A resistor should be connected between this pin and GND. Used to set the current. |  |  |

| I/O                                                   | Input/Output.                                                                                                                                 |  |  |

| IMn                                                   | Interface mode select pin. (Where <i>n</i> is the corresponding number.)                                                                      |  |  |

| IS1<br>BS1<br>C86                                     | IS1 IS2 Interface Mode                                                                                                                        |  |  |

| M80                                                   | 0 0 SPI (Serial), if available                                                                                                                |  |  |

| IS2<br>BS2                                            | 0 1 6800 Parallel, if available                                                                                                               |  |  |

| P/S<br>MS                                             | 1 0 Not Allowed                                                                                                                               |  |  |

| MS<br>M/S#                                            | 1 1 8080 Parallel                                                                                                                             |  |  |

| L <sub>BRNORMAL</sub><br>IV                           | Luminous Intensity Brightness, NORMAL operation.                                                                                              |  |  |

| L <sub>BRSTANDBY</sub><br>IV                          | Luminous Intensity Brightness, STANDBY.                                                                                                       |  |  |

| mm                                                    | Millimeter or millimetre. Unit of length equal to one thousandth of a meter.<br>1 millimeter = 0.0394 inches.                                 |  |  |

| mW                                                    | Milliwatt is equal to one thousandth of a Watt.<br>Watts = Volts x Amps.                                                                      |  |  |

| NC<br>nc                                              | Make no connection.                                                                                                                           |  |  |

| OLED                                                  | Organic light-emitting diode.                                                                                                                 |  |  |

| P <sub>OPERATION</sub><br>P <sub>T</sub>              | Normal mode Power consumption.                                                                                                                |  |  |

| P <sub>STANDBY</sub>                                  | Standby mode Power consumption.                                                                                                               |  |  |

| Symbol                                                                                    | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q                                                                                         | Transistor, including FET and MOSFET.                                                                                                                                                                                                                                                                                                                                                       |