# HT1647

## 4-Level Gray Scale 64×16 LCD Controller for I/O MCU

### **Technical Document**

- FAQs

- Application Note

### **Features**

- Operating voltage: 2.7V~5.2V

- · Built-in 32kHz RC oscillator

- External 32.768kHz crystal oscillator or 32kHz frequency source input

- Standby current: < 1μA at 3V, < 2μA at 5V</li>

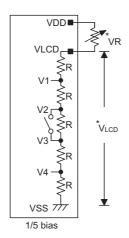

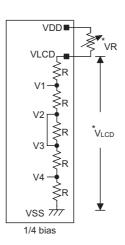

- Internal resistor type: 1/5 bias or 1/4 bias, 1/16 duty

- Two selectable LCD frame frequencies: 89Hz or

- Max. 64×16 patterns, 64 segments and 16 commons

- Built-in bit-map display RAM: 2048 bits (=64×16×2

- · Built-in internal resistor type bias generator

- · Six-wire interface (four data wires)

- Eight kinds of time base/WDT selection

- · Time base or WDT overflow output

- R/W address auto increment

- Built-in buzzer driver (2kHz/4kHz)

- Power down command reduces power consumption

- Software configuration feature

- Data mode and Command mode instructions

- · Three data accessing modes

- · Provides VLCD pin to adjust LCD operating voltage

- · Provides three kinds of bias current programming

- Control of TN-type, STN-type LCDs and ECB-type

- · Four-level gray scale output for TN-type, STN-type LCDs panel

- Four-color output for ECB-type LCDs panel

- · 100-pin QFP package and in chip form

## **Applications**

- · Leisure products

- Games

- · Personal digital assistant

- · Cellular phone

- Global positioning system

- Consumer electronics

## **General Description**

HT1647 is a peripheral device specially designed for I/O type MCU used to expand the display capability. The max. display segment of the device are 1024 patterns (64 segments and 16 commons). It also supports four data bits interface, buzzer sound, Watchdog Timer or time base timer functions. The HT1647 is a memory mapping and multi-function LCD controller. Since the HT1647 can control ECB-type (Electrically Controlled Birefringence) LCDs in addition to current TN-type (Twisted Nematic) or STN-type (Super Twisted Nematic) LCDs, it can support 4-color display as well as

4-level gray scale display. It displays 4-level gray scale output when the HT1647 drives a TN-type, STN-type LCDs. It displays four color output when the HT1647 drives an ECB-type. HT1647 uses PWM (Pulse Width Modulation) technique. The software configuration feature of the HT1647 make it suitable for multiple LCD applications including LCD modules and display subsystems. Only six lines (CS, WR, DB0~DB3) are required for the interface between the host controller and the HT1647.

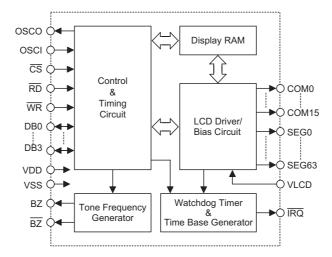

## **Block Diagram**

Note:  $\overline{CS}$ : Chip selection

BZ,  $\overline{BZ}$ : Tone outputs

WR,  $\overline{RD}$ : WRITE clock, READ clock

DB0~DB3: Data bus

COM0~COM15, SEG0~SEG63: LCD outputs  $\overline{IRQ}$ : Time base or WDT overflow output

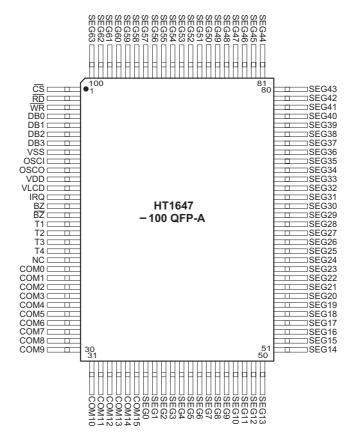

## **Pin Assignment**

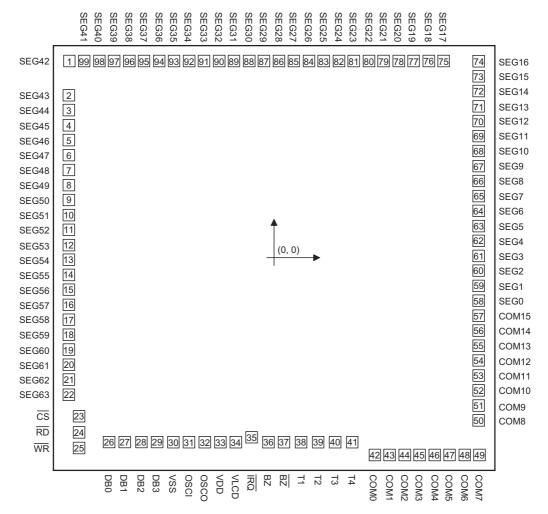

## **Pad Assignment**

Chip size:  $3865 \times 3770 \, (\mu m)^2$

## Pad Coordinates Unit: μm

| Pad No. | Х        | Υ       | Pad No. | Х       | Υ        | Pad No. | Х       | Υ       |

|---------|----------|---------|---------|---------|----------|---------|---------|---------|

| 1       | -1774.50 | 1708.30 | 34      | -331.40 | -1600.00 | 67      | 1775.70 | 795.30  |

| 2       | -1779.30 | 1409.80 | 35      | -194.50 | -1558.30 | 68      | 1775.70 | 927.10  |

| 3       | -1779.30 | 1281.80 | 36      | -48.00  | -1600.00 | 69      | 1775.70 | 1055.10 |

| 4       | -1779.30 | 1150.00 | 37      | 87.40   | -1600.00 | 70      | 1775.70 | 1186.90 |

| 5       | -1779.30 | 1022.00 | 38      | 235.20  | -1600.00 | 71      | 1775.70 | 1314.90 |

| 6       | -1779.30 | 890.20  | 39      | 383.40  | -1600.00 | 72      | 1775.70 | 1446.70 |

| 7       | -1779.30 | 762.20  | 40      | 530.40  | -1600.00 | 73      | 1775.70 | 1574.70 |

| 8       | -1779.30 | 630.40  | 41      | 678.60  | -1600.00 | 74      | 1775.70 | 1706.50 |

| 9       | -1779.30 | 502.40  | 42      | 875.00  | -1712.30 | 75      | 1471.10 | 1708.30 |

| 10      | -1779.30 | 370.60  | 43      | 1003.00 | -1712.30 | 76      | 1343.10 | 1708.30 |

| 11      | -1779.30 | 242.60  | 44      | 1134.80 | -1712.30 | 77      | 1211.30 | 1708.30 |

| 12      | -1779.30 | 110.80  | 45      | 1262.80 | -1712.30 | 78      | 1083.30 | 1708.30 |

| 13      | -1779.30 | -17.20  | 46      | 1394.60 | -1712.30 | 79      | 951.50  | 1708.30 |

Rev. 1.30 3 November 10, 2005

<sup>\*</sup> The IC substrate should be connected to VSS in the PCB layout artwork.

| Pad No. | Х        | Υ        | Pad No. | Х       | Υ        | Pad No. | Х        | Υ       |

|---------|----------|----------|---------|---------|----------|---------|----------|---------|

| 14      | -1779.30 | -149.00  | 47      | 1522.60 | -1712.30 | 80      | 823.50   | 1708.30 |

| 15      | -1779.30 | -277.00  | 48      | 1654.40 | -1712.30 | 81      | 691.70   | 1708.30 |

| 16      | -1779.30 | -408.80  | 49      | 1782.40 | -1712.30 | 82      | 563.70   | 1708.30 |

| 17      | -1779.30 | -536.80  | 50      | 1775.70 | -1411.10 | 83      | 431.90   | 1708.30 |

| 18      | -1779.30 | -668.60  | 51      | 1775.70 | -1283.10 | 84      | 303.90   | 1708.30 |

| 19      | -1779.30 | -796.60  | 52      | 1775.70 | -1151.30 | 85      | 172.10   | 1708.30 |

| 20      | -1779.30 | -928.80  | 53      | 1775.70 | -1023.30 | 86      | 44.10    | 1708.30 |

| 21      | -1779.30 | -1056.80 | 54      | 1775.70 | -891.50  | 87      | -87.70   | 1708.30 |

| 22      | -1779.30 | -1189.00 | 55      | 1775.70 | -763.50  | 88      | -215.70  | 1708.30 |

| 23      | -1690.00 | -1375.40 | 56      | 1775.70 | -631.70  | 89      | -347.50  | 1708.30 |

| 24      | -1690.00 | -1515.40 | 57      | 1775.70 | -503.70  | 90      | -475.50  | 1708.30 |

| 25      | -1690.00 | -1651.00 | 58      | 1775.70 | -371.90  | 91      | -607.30  | 1708.30 |

| 26      | -1430.20 | -1599.90 | 59      | 1775.70 | -243.90  | 92      | -735.30  | 1708.30 |

| 27      | -1294.80 | -1599.90 | 60      | 1775.70 | -112.10  | 93      | -867.10  | 1708.30 |

| 28      | -1149.50 | -1599.90 | 61      | 1775.70 | 15.90    | 94      | -995.10  | 1708.30 |

| 29      | -1013.90 | -1599.90 | 62      | 1775.70 | 147.70   | 95      | -1126.90 | 1708.30 |

| 30      | -872.80  | -1600.00 | 63      | 1775.70 | 275.70   | 96      | -1254.90 | 1708.30 |

| 31      | -738.30  | -1600.00 | 64      | 1775.70 | 407.50   | 97      | -1386.70 | 1708.30 |

| 32      | -600.10  | -1600.00 | 65      | 1775.70 | 535.50   | 98      | -1514.70 | 1708.30 |

| 33      | -465.60  | -1600.00 | 66      | 1775.70 | 667.30   | 99      | -1646.50 | 1708.30 |

# **Pad Description**

| Pad No.        | Pad Name      | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23             | <del>CS</del> | I   | Chip selection input with pull-high resistor. When the $\overline{\text{CS}}$ is logic high, the data and command read from or write to the HT1647 are disabled. The serial interface circuit is also reset. But if the $\overline{\text{CS}}$ is at a logic low level and is input to the $\overline{\text{CS}}$ pad, the data and command transmission between the host controller and the HT1647 are all enabled. |

| 24             | RD            | I   | READ clock input with pull-high resistor. Data in the RAM of the HT1647 are clocked out on the rising edge of the $\overline{RD}$ signal. The clocked out data will appear on the data line. The host controller can use the next falling edge to latch the clocked out data.                                                                                                                                        |

| 25             | WR            | I   | WRITE clock input with pull-high resistor. Data on the DATA line are latched into the HT1647 on the rising edge of the WR signal.                                                                                                                                                                                                                                                                                    |

| 26~29          | DB0~DB3       | I/O | Parallel data input/output with a pull-high resistor                                                                                                                                                                                                                                                                                                                                                                 |

| 30             | VSS           | _   | Negative power supply for logic circuit, ground                                                                                                                                                                                                                                                                                                                                                                      |

| 31             | OSCI          | I   | The OSCI and OSCO pads are connected to a 32.768kHz crystal in order to                                                                                                                                                                                                                                                                                                                                              |

| 32             | osco          | 0   | generate a system clock. If the system clock comes from an external clock source, the external clock source should be connected to the OSCI pad. But if an on-chip RC oscillator is selected, the OSCI and OSCO pads can be left open.                                                                                                                                                                               |

| 33             | VDD           | _   | Positive power supply for logic circuit                                                                                                                                                                                                                                                                                                                                                                              |

| 34             | VLCD          | ı   | Power supply for LCD driver circuit                                                                                                                                                                                                                                                                                                                                                                                  |

| 35             | ĪRQ           | 0   | Time base or Watchdog Timer overflow flag, NMOS open drain output.                                                                                                                                                                                                                                                                                                                                                   |

| 36, 37         | BZ, BZ        | 0   | 2kHz or 4kHz frequency output pair (tristate output buffer)                                                                                                                                                                                                                                                                                                                                                          |

| 38~41          | T1~T4         | I   | Not connected                                                                                                                                                                                                                                                                                                                                                                                                        |

| 42~57          | COM0~COM15    | 0   | LCD common outputs                                                                                                                                                                                                                                                                                                                                                                                                   |

| 58~99,<br>1~22 | SEG0~SEG63    | 0   | LCD segment outputs                                                                                                                                                                                                                                                                                                                                                                                                  |

## **Absolute Maximum Ratings**

| Supply VoltageV <sub>SS</sub> -0.3V to V <sub>SS</sub> +5.5V | Storage Temperature50°C to 125°C  |

|--------------------------------------------------------------|-----------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V to V <sub>DD</sub> +0.3V  | Operating Temperature25°C to 75°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

## D.C. Characteristics Ta=25°C

| Symbol            | Parameter                   |          | Test Conditions          | Min.    | Trees | Max  | Unit |

|-------------------|-----------------------------|----------|--------------------------|---------|-------|------|------|

| Symbol            | Farameter                   | $V_{DD}$ | Conditions               | IVIIII. | Тур.  | Max. | Onit |

| $V_{DD}$          | Operating Voltage           | _        | _                        | 2.7     | _     | 5.2  | V    |

|                   | 0                           | 3V       | No load/LCD ON           | _       | 150   | 250  | μА   |

| I <sub>DD1</sub>  | Operating Current           | 5V       | On-chip RC oscillator    | _       | 250   | 370  | μА   |

|                   | O a servet in an O amount   | 3V       | No load/LCD ON           | _       | 135   | 200  | μА   |

| I <sub>DD2</sub>  | Operating Current           | 5V       | Crystal oscillator       | _       | 200   | 300  | μА   |

| 1                 | Operating Current           | 3V       | No load/LCD OFF          | _       | 15    | 30   | μА   |

| I <sub>DD11</sub> | Operating Current           | 5V       | On-chip RC oscillator    | _       | 50    | 70   | μА   |

| l                 | Operating Current           | 3V       | No load/LCD OFF          | _       | 2     | 10   | μΑ   |

| I <sub>DD22</sub> | Operating Current           | 5V       | Crystal oscillator       | _       | 3     | 10   | μΑ   |

| l                 | Standby Current             | 3V       | No load Power down made  | _       | _     | 1    | μΑ   |

| I <sub>STB</sub>  | Standby Current             | 5V       | No load, Power down mode | _       | _     | 2    | μΑ   |

| $V_{IL}$          | Input Low Voltage           | 3V       | DB0~DB3, WR, CS, RD      | 0       | _     | 0.6  | V    |

| V IL              | Input Low Voltage           | 5V       | D60~D63, WK, C3, KD      | 0       | _     | 1.0  | V    |

| V <sub>IH</sub>   | Input High Voltage          | 3V       | DB0~DB3, WR, CS, RD      | 2.4     | _     | 3    | V    |

| VIH               | Input High Voltage          | 5V       | D60~D63, WK, C3, KD      | 4.0     | _     | 5    | V    |

| la                | BZ, BZ, IRQ Sink Current    | 3V       | V <sub>OL</sub> =0.3V    | 1.2     | 2.5   | _    | mA   |

| I <sub>OL1</sub>  | bz, bz, ikg sliik cuiteiit  | 5V       | V <sub>OL</sub> =0.5V    | 3       | 6     | _    | mA   |

| I <sub>OH1</sub>  | BZ, BZ Source Current       | 3V       | V <sub>OH</sub> =2.7V    | -0.9    | -1.8  | —    | mA   |

| 'OH1              | bz, bz source current       | 5V       | V <sub>OH</sub> =4.5V    | -2      | -4    | _    | mA   |

| I <sub>OL2</sub>  | DB0~DB3 Sink Current        | 3V       | V <sub>OL</sub> =0.3V    | 1.2     | 2.5   | —    | mA   |

| IOL2              | DB0*DB3 Silik Cullelit      | 5V       | V <sub>OL</sub> =0.5V    | 3       | 6     | _    | mA   |

| I <sub>OH2</sub>  | DB0~DB3 Source Current      | 3V       | V <sub>OH</sub> =2.7V    | -0.9    | -1.8  | —    | mA   |

| IOH2              | DB0*DB3 Source Current      | 5V       | V <sub>OH</sub> =4.5V    | -2      | -4    | _    | mA   |

| I <sub>OL3</sub>  | LCD Common Sink Current     | 3V       | V <sub>OL</sub> =0.3V    | 80      | 160   | _    | μΑ   |

| IOL3              | LCD Common Sink Current     | 5V       | V <sub>OL</sub> =0.5V    | 180     | 360   | _    | μΑ   |

| I <sub>OH3</sub>  | LCD Common Source Current   | 3V       | V <sub>OH</sub> =2.7V    | -40     | -80   | _    | μΑ   |

| ЮПЗ               | EOD COMMON COURCE CUNTON    | 5V       | V <sub>OH</sub> =4.5V    | -90     | -180  | _    | μΑ   |

| I <sub>OL4</sub>  | LCD Segment Sink Current    | 3V       | V <sub>OL</sub> =0.3V    | 50      | 100   | _    | μΑ   |

| ·OL4              | LOD OCGINENT ONK OUTCH      | 5V       | V <sub>OL</sub> =0.5V    | 120     | 240   | _    | μΑ   |

| I <sub>OH4</sub>  | LCD Segment Source Current  | 3V       | V <sub>OH</sub> =2.7V    | -30     | -60   | _    | μΑ   |

| •ОП4              | 200 Ooginent Oodice Odirent | 5V       | V <sub>OH</sub> =4.5V    | -70     | -140  | _    | μΑ   |

| R <sub>PH</sub>   | Pull-high Resistor          | 3V       | DB0~DB3, WR, CS, RD      | 150     | 250   | 410  | kΩ   |

| KPH               | - Gir-riigit (COIStOI       | 5V       | DD0, VVIX, OO, IXD       | 60      | 125   | 210  | kΩ   |

Rev. 1.30 5 November 10, 2005

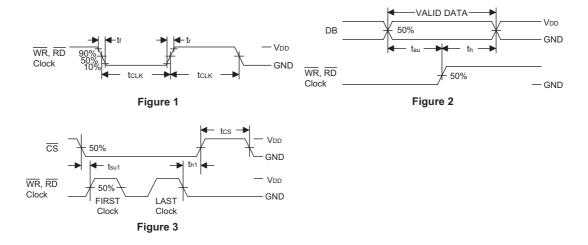

## A.C. Characteristics

Ta=25°C

| 0                               | Down to a                                                                                     |      | Test Conditions            | M      | T                  | Mari    | 114  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------|------|----------------------------|--------|--------------------|---------|------|--|

| Symbol                          | Parameter                                                                                     |      | Conditions                 | Min.   | Тур.               | Max.    | Unit |  |

| r                               | System Clock                                                                                  |      | On this DO and Water       | 22     | 32                 | 40      | kHz  |  |

| TSYS1                           |                                                                                               |      | On-chip RC oscillator      | 24     | 32                 | 40      | kHz  |  |

| r                               | 0 ( 0                                                                                         | 3V   | On a fall and illustration | _      | 32.768             | _       | kHz  |  |

| f <sub>SYS2</sub>               | System Clock                                                                                  | 5V   | Crystal oscillator         | _      | 32.768             | _       | kHz  |  |

|                                 |                                                                                               | 3V   |                            | _      | 32                 | _       | kHz  |  |

| f <sub>SYS3</sub>               | System Clock                                                                                  | 5V   | External clock source      | _      | 32                 | _       | kHz  |  |

| ,                               |                                                                                               | 3V   |                            | 61/117 | 89/170             | 111/213 | Hz   |  |

| f <sub>LCD1</sub>               | LCD Frame Frequency                                                                           | 5V   | On-chip RC oscillator      | 61/117 | 89/170             | 111/213 | Hz   |  |

| ,                               |                                                                                               | 3V   |                            | _      | 64                 | _       | Hz   |  |

| f <sub>LCD2</sub>               | LCD Frame Frequency                                                                           | 5V   | Crystal oscillator         | _      | 64                 | _       | Hz   |  |

| _                               |                                                                                               |      |                            | _      | 64                 | _       | Hz   |  |

| f <sub>LCD3</sub>               | LCD Frame Frequency                                                                           | 5V   | External clock source      | _      | 64                 | _       | Hz   |  |

| t <sub>COM</sub>                | LCD Common Period                                                                             | _    | n: Number of COM           | _      | n/f <sub>LCD</sub> | _       | sec  |  |

| _                               |                                                                                               | 3V   |                            | _      | _                  | 150     | kHz  |  |

| f <sub>CLK1</sub>               | 4-Bit Data Clock (WR Pin)                                                                     | 5V   | Duty cycle 50%             | _      | _                  | 300     | kHz  |  |

|                                 |                                                                                               | 3V   |                            |        | _                  | 75      | kHz  |  |

| f <sub>CLK2</sub>               | 4-Bit Data Clock (RD Pin)                                                                     |      | Duty cycle 50%             |        | _                  | 150     | kHz  |  |

| t <sub>CS</sub>                 | 4-Bit Interface Reset Pulse Width (Figure 3)                                                  | _    | CS                         | _      | 250                | _       | ns   |  |

|                                 | WR, RD Input Pulse Width (Figure 1)                                                           | 2) ( | Write mode                 | 3.34   |                    |         |      |  |

|                                 |                                                                                               | 3V   | Read mode                  | 6.67   | _                  | _       | μS   |  |

| t <sub>CLK</sub>                |                                                                                               | 5V   | Write mode                 | 1.67   |                    |         | _    |  |

|                                 |                                                                                               |      | Read mode                  | 3.34   | _                  |         | μS   |  |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time Serial Data Clock                                                              | 3V   |                            |        | 120                |         | ns   |  |

| प, प                            | Width (Figure 1)                                                                              | 5V   | _                          |        | 120                |         | 115  |  |

| t <sub>su</sub>                 | Setup Time for DB to WR, RD Clock                                                             | 3V   |                            |        | 120                |         | ns   |  |

| -su                             | Width (Figure 2)                                                                              | 5V   |                            |        | 120                |         | 110  |  |

| t <sub>h</sub>                  | Hold Time for DB to WR, RD Clock                                                              | 3V   | _                          | _      | 120                |         | ns   |  |

| -11                             | Width (Figure 2)                                                                              | 5V   |                            |        |                    |         |      |  |

| t <sub>su1</sub>                | Setup Time for CS to WR, RD Clock                                                             |      | _                          | _      | 100                | _       | ns   |  |

|                                 | Width (Figure 3)                                                                              | 5V   |                            |        |                    |         |      |  |

| t <sub>h1</sub>                 | Hold Time for $\overline{\text{CS}}$ to $\overline{\text{WR}}$ , $\overline{\text{RD}}$ Clock |      | _                          | _      | 100                | _       | ns   |  |

| 4N1                             | Width (Figure 3)                                                                              | 5V   |                            |        | 100                |         |      |  |

## **Functional Description**

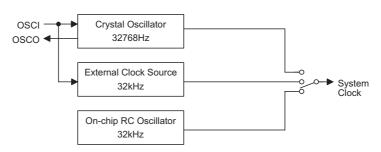

### **System Oscillator**

The HT1647 system clock is used to generate the time base/Watchdog Timer (WDT) clock frequency, LCD driving clock, and tone frequency. The clock source may be from an on-chip RC oscillator (32kHz), a crystal oscillator (32.768kHz), or an external 32kHz clock by the S/W setting. The configuration of the system oscillator is as shown. After the SYS DIS command is executed, the system clock will stop and the LCD bias generator will turn off. That command is available only for the on-chip RC oscillator or for the crystal oscillator. Once the system clock stops, the LCD display will become blank, and the time base/WDT loses its function as well

The LCD OFF command is used to turn the LCD bias generator off. After the LCD bias generator switches off by issuing the LCD OFF command, using the SYS DIS command reduces power consumption, thus serving as

a system power down command. But if the external clock source is chosen as the system clock, using the SYS DIS command can neither turn the oscillator off nor carry out the power down mode. The crystal oscillator option can be applied to connect an external frequency source of 32kHz to the OSCI pin. In this case, the system fails to enter the power down mode, similar to the case in the external 32kHz clock source operation. At the initial system power on, the HT1647 is at the SYS DIS state.

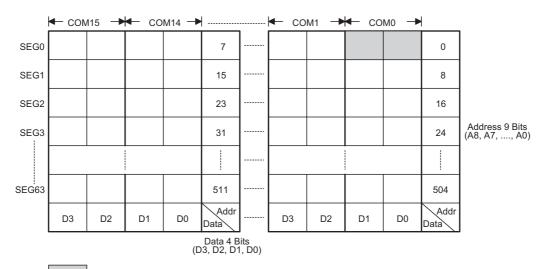

### **Display Memory - RAM Structure**

The static display RAM is organized into 512×4 bits and stores the display data. The contents of the RAM are directly mapped to the contents of the LCD driver. Data in the RAM can be accessed by the READ, WRITE and READ-MODIFY-WRITE commands. The following is a mapping from the RAM to the LCD patterns.

**System Oscillator Configuration**

: Two bits of RAM map to LCD's one pixel and decide 4-level gray scale or 4-color display concurrently.

**Display Memory - RAM Structure**

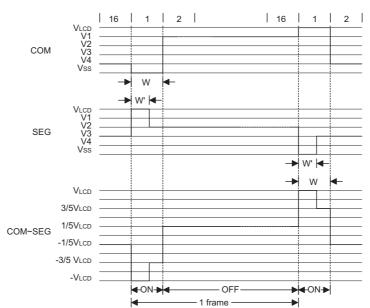

## **Gray Scale Level Decision**

HT1647 uses PWM technique to provide 4-level gray scale display. Two bits of RAM data code ((D3, D2) or (D1, D0)) decide one pixel level of LCDs, level 1~level divided by 4. Every level must be defined as one kind of gray scale by PWM data (namely B4~B0) previously.

| RAM Data Code<br>(D3, D2) or (D1, D0) | Choice Gray Scale Level |

|---------------------------------------|-------------------------|

| (1, 1)                                | Level 1                 |

| (1, 0)                                | Level 2                 |

| (0, 1)                                | Level 3                 |

| (0, 0)                                | Level 4                 |

**RAM Data Defined Gray Scale Level**

## Frame Frequency

HT1647 provides two kinds of frame frequency option by command code; 89Hz and 170Hz respectively. FRAME 89Hz provides 89Hz frame frequency and active segment signal width can be divided into 24 sections concurrently. FRAME 170Hz provides 170Hz frame frequency and active segment signal width can be divided into 13 sections concurrently. The 24 sections display a particularly gray scale more than the 13 sections by PWM data. The default is FRAME 89Hz.

## **Gray Scale Display**

If the user choose 89Hz frame frequency, a max. of 24 sections can be programmed to suit a satisfactory gray scale in every level. Similarly, if the user choose 170Hz frame frequency, a max. of 13 sections can be programmed to suit a satisfactory gray scale in every level. HT1647 provides 5-bit PWM data to control the length of the section. In other words, a max. Of 24 gray scales are generated by 5-bit binary PWM data. At FRAME 89Hz mode, the HT1647 only provides a max. of 24 adjustable gray scales although 32 is the expressed max. value by 5 bits binary code. When 5 bits binary code value is more than 23, the PWM control circuit uniformly regards 23. To increase PWM data indicates to increase the length of the active segment signal. The varied length of the active segment signal displays varied gray scale in TN-type, STN-type LCDs (refer to table 1). Similarly, it displays varied color in ECB-type LCDs. The color display is derived from ECB-type LCD specification. At FRAME 170Hz mode, the HT1647 only provides a max. of 13 adjustable gray scales although 32 is the expressed max. value by 5 bits binary code. When the 5 bits binary code value is more than 12, the PWM control circuit uniformly regards 12. The user must appoint four kinds of PWM data to four kinds of different gray scale level by commanding PWM data (refer to table 2).

| Name        | Command Code                 | Function                                                                                     |

|-------------|------------------------------|----------------------------------------------------------------------------------------------|

| FRAME 170Hz | X100-0001-1000-XXXX          | Select 170Hz frame frequency and active segment signal width can be divided into 13 sections |

| FRAME 89Hz  | X <b>100</b> -0001-1101-XXXX | Select 89Hz frame frequency and active segment signal width can be divided into 24 sections  |

Frame Frequency Selection Command Code

Rev. 1.30 8 November 10, 2005

## Relationship Table between PWM Data and Gray Scale

| Value          | 5  | bits l | PWIV | l dat | а  | PWM<br>(ON width) | Gray Scale |

|----------------|----|--------|------|-------|----|-------------------|------------|

|                | B4 | B3     | B2   | B1    | B0 | ,                 |            |

| 0              | 0  | 0      | 0    | 0     | 0  | 0 (0/23)          |            |

| 1              | 0  | 0      | 0    | 0     | 1  | 1/23              |            |

| 3              | 0  | 0      | 0    | 1     | 0  | 2/23              |            |

|                | 0  | 0      | 0    | 1     | 1  | 3/23              |            |

| 4              | 0  | 0      | 1    | 0     | 0  | 4/23              |            |

| 5              | 0  | 0      | 1    | 0     | 1  | 5/23              |            |

| 6              | 0  | 0      | 1    | 1     | 0  | 6/23              |            |

| 7              | 0  | 0      | 1    | 1     | 1  | 7/23              |            |

| 8              | 0  | 1      | 0    | 0     | 0  | 8/23<br>9/23      |            |

| 9              | 0  | 1      | 0    | 0     | 1  | 9/23              |            |

| 10             | 0  | 1      | 0    | 1     | 0  | 10/23             |            |

| 11             | 0  | 1      | 0    | 1     | 1  | 11/23             |            |

| 12             | 0  | 1      | 1    | 0     | 0  | 12/23             |            |

| 13             | 0  | 1      | 1    | 0     | 1  | 13/23             |            |

| 14             | 0  | 1      | 1    | 1     | 0  | 14/23             |            |

| 15             | 0  | 1      | 1    | 1     | 1  | 15/23             |            |

| 16             | 1  | 0      | 0    | 0     | 0  | 16/23             |            |

| 17             | 1  | 0      | 0    | 0     | 1  | 17/23             |            |

| 18             | 1  | 0      | 0    | 1     | 0  | 18/23             |            |

| 19             | 1  | 0      | 0    | 1     | 1  | 19/23             |            |

| 20             | 1  | 0      | 1    | 0     | 0  | 20/23             |            |

| 21             | 1  | 0      | 1    | 0     | 1  | 21/23             |            |

| 22             | 1  | 0      | 1    | 1     | 0  | 22/23             |            |

| 21<br>22<br>23 | 1  | 0      | 1    | 1     | 1  | 1 (23/23)         |            |

| 24             | 1  | 1      | 0    | 0     | 0  | 1 (24/23)         |            |

|                |    |        |      |       |    |                   |            |

| 31             | 1  | 1      | 1    | 1     | 1  | 1 (31/23)         |            |

Table 1: FRAME 89Hz Mode

| Value | 5  | bits | PWN | l dat | а  | PWM        | Gray Scale       |

|-------|----|------|-----|-------|----|------------|------------------|

|       | B4 | B3   | B2  | B1    | B0 | (ON width) | , and the second |

| 0     | 0  | 0    | 0   | 0     | 0  | 0 (0/12)   |                  |

| 1     | 0  | 0    | 0   | 0     | 1  | 1/12       |                  |

| 2     | 0  | 0    | 0   | 1     | 0  | 2/12       |                  |

| 3     | 0  | 0    | 0   | 1     | 1  | 3/12       |                  |

| 4     | 0  | 0    | 1   | 0     | 0  | 4/12       |                  |

| 5     | 0  | 0    | 1   | 0     | 1  | 5/12       |                  |

| 6     | 0  | 0    | 1   | 1     | 0  | 6/12       |                  |

| 7     | 0  | 0    | 1   | 1     | 1  | 7/12       |                  |

| 8     | 0  | 1    | 0   | 0     | 0  | 8/12       |                  |

| 9     | 0  | 1    | 0   | 0     | 1  | 9/12       |                  |

| 10    | 0  | 1    | 0   | 1     | 0  | 10/12      |                  |

| 11    | 0  | 1    | 0   | 1     | 1  | 11/12      |                  |

| 12    | 0  | 1    | 1   | 0     | 0  | 1 (12/12)  |                  |

| 13    | 0  | 1    | 1   | 0     | 1  | 1 (13/12)  |                  |

|       |    |      |     |       |    |            |                  |

| 31    | 1  | 1    | 1   | 1     | 1  | 1 (31/12)  |                  |

Table 2: FRAME 170Hz Mode

Note: The varied PWM data displays various gray scale in TN-type, STN-type LCDs.

The color display derives from ECB-type LCD's specification.

| Name        | Command Code                          | Function                           |

|-------------|---------------------------------------|------------------------------------|

| GRS LEVEL 1 | X <b>100</b> -001 B4-B3 B2 B1 B0-XXXX | Set PWM data in gray scale level 1 |

| GRS LEVEL 2 | X <b>100</b> -010 B4-B3 B2 B1 B0-XXXX | Set PWM data in gray scale level 2 |

| GRS LEVEL 3 | X <b>100</b> -011 B4-B3 B2 B1 B0-XXXX | Set PWM data in gray scale level 3 |

| GRS LEVEL 4 | X <b>100</b> -100 B4-B3 B2 B1 B0-XXXX | Set PWM data in gray scale level 4 |

Four Kinds of Gray Scale Level Command Code

Note: "W" Real active segment signal width (adjustable width by PWM data) "W" Max. active segment signal width PWM (ON width): W'/W, 0≤W'/W≤1 (refer to table 1 & tabel 2)

Example of Waveform (B Type) in 1/5 Bias, 1/16 Duty Cycle Drive

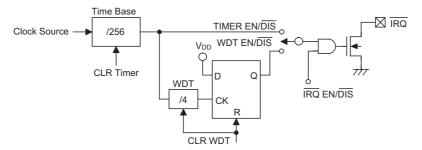

### Time Base and Watchdog Timer - WDT

The time base generator and WDT share the same counter which is divided by 256. The  $\overline{\text{IRQ}}$  clock can be programmed as 1Hz, 2Hz, ...., 128Hz output. TIMER DIS/EN/CLR, WDT DIS/EN/CLR and  $\overline{\text{IRQ}}$  EN/DIS are independent from each other. Once the WDT time-out occurs, the  $\overline{\text{IRQ}}$  pin will remain at a logic low level until the CLR WDT or the  $\overline{\text{IRQ}}$  DIS command is issued.

If an external clock is selected as the system frequency source, the SYS DIS command turns out invalid and the power down mode fails to be carried out until the external clock source is removed.

### **Buzzer Tone Output**

A simple tone generator is implemented in the HT1647. The tone generator can output a pair of differential driving signals on the BZ and  $\overline{\text{BZ}}$  which are used to generate a single tone.

By executing the TONE 4K and TONE 2K commands there are two tone frequency outputs selectable that can turn on the tone output. The TONE 4K and TONE 2K commands set the tone frequency to 4kHz and 2kHz, respectively. The tone output can be turned off by invoking the TONE OFF command. The tone outputs, namely BZ and  $\overline{\text{BZ}}$ , are a pair of differential driving outputs used to drive a piezo buzzer. Once the system is disabled or the tone output is inhibited, the BZ and the  $\overline{\text{BZ}}$  outputs will remain at low level.

#### Command Format

The HT1647 can be configured by software setting. There are two mode commands to configure the HT1647 resource and to transfer the LCD display data.

The configuration mode of the HT1647 is called command mode, and its command mode ID is 100. The command mode consists of a system configuration command, a system frequency selection command, an LCD configuration command, a tone frequency selection command, a bias current selection command, a gray scale level selection command, a timer/WDT setting command, and an operating command. The data mode, on the other hand, includes READ, WRITE, and READ-MODIFY-WRITE operations.

The following are the data mode ID and the command mode ID:

| Operation         | Mode    | ID  |

|-------------------|---------|-----|

| READ              | Data    | 110 |

| WRITE             | Data    | 101 |

| READ-MODIFY-WRITE | Data    | 101 |

| COMMAND           | Command | 100 |

If successive commands have been issued, the command mode ID can be omitted. While the system is operating in the non-successive command or the non-successive address data mode, the  $\overline{\text{CS}}$  pin should be set to "1" and the previous operation mode will also be reset. The  $\overline{\text{CS}}$  pin returns to "0", so a new operation mode ID should be issued first.

**Time Base and WDT Configurations**

| Name     | Command Code                | Function                                    |

|----------|-----------------------------|---------------------------------------------|

| TONE OFF | <b>X100</b> -0000-1000-XXXX | Turn-off tone output                        |

| TONE 4K  | X100-0001-0000-XXXX         | Turn-on tone output, tone frequency is 4kHz |

| TONE 2K  | X100-0001-0001-XXXX         | Turn-on tone output, tone frequency is 2kHz |

**Buzzer Tone Output Command Code**

Rev. 1.30 10 November 10, 2005

#### **Bias Generator**

The HT1647 bias voltage belongs to internal resistor type. It provides two kinds of bias option named 1/5 bias and 1/4 bias respectively. It is recommended to select 1/5 bias to fit TN-type, STN-type LCDs and select 1/4 bias to fit ECB-type LCDs. It also provides three kinds of bias current option by programming to suitably drive an LCD panel. The three kinds of bias current are large,

middle, and small, respectively. Usually, large panel LCD can be excellently displayed by large bias current. Relatively, it consumes large current when LCD ON command is used. Small bias current provides low power consumption during On condition when the LCD is normally displayed. The following are the reference value table.

| V <sub>LCD</sub> | Bias | Large Bias Current | Middle Bias Current | Small Bias Current |

|------------------|------|--------------------|---------------------|--------------------|

| 4V               | 1/5  | 300μΑ              | 100μΑ               | 40μΑ               |

| 4V               | 1/4  | 375μΑ              | 125μΑ               | 50μΑ               |

- \* The voltage applied to VLCD pin must be lower than VDD

- \* Adjust VR to fit LCD display, at VDD=5V, VLCD=4V, VR=15k $\Omega\pm20\%$

**Internal Resistor Type Bias Generator Configurations**

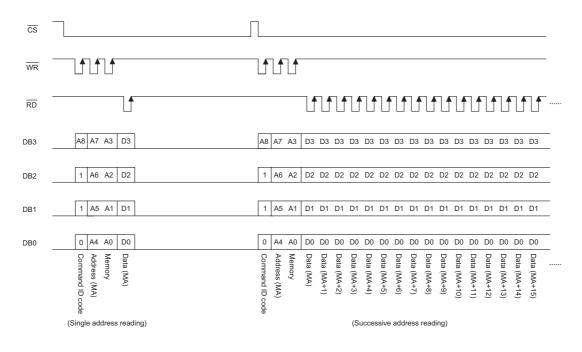

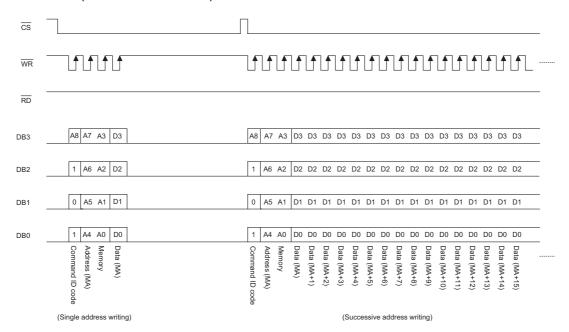

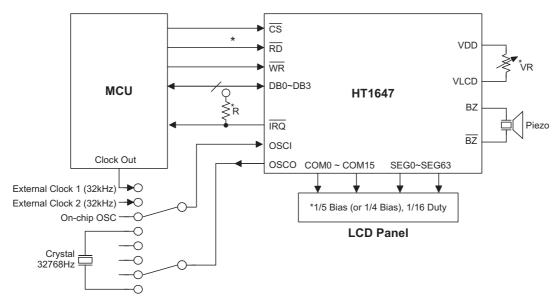

### Interfacing

Only six lines are required to interface with the HT1647. The  $\overline{CS}$  line is used to initialize the serial interface circuit and to terminate the communication between the host controller and the HT1647. If the  $\overline{CS}$  pin is set to 1, the data and command issued between the host controller and the HT1647 are first disabled and then initialized. Before issuing a mode command or mode switching, a high level pulse is required to initialize the serial interface of the HT1647. The DB0~DB3 are the 4-bit parallel data input/output lines. Data to be read or written or commands to be written have to pass through the DB0~DB3 lines. The  $\overline{RD}$  line is the READ clock input. Data in the RAM are clocked out on the falling edge of the

$\overline{\text{RD}}$  signal, and the clocked out data will then appear on the DB0~DB3 lines. It is recommended that the host controller read correct data during the interval between the rising edge and the next falling edge of the  $\overline{\text{RD}}$  signal. The  $\overline{\text{WR}}$  line is the WRITE clock input. The data, address, and command on the DB0~DB3 lines are all clocked into the HT1647 on the rising edge of the  $\overline{\text{WR}}$  signal. There is an optional  $\overline{\text{IRQ}}$  line to be used as an interface between the host controller and the HT1647. The  $\overline{\text{IRQ}}$  pin can be selected as a timer output or a WDT overflow flag output by the S/W setting. The host controller can perform the time base or the WDT function by connecting with the  $\overline{\text{IRQ}}$  pin of the HT1647.

Rev. 1.30 11 November 10, 2005

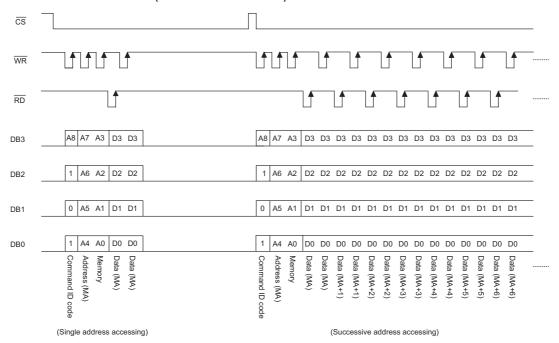

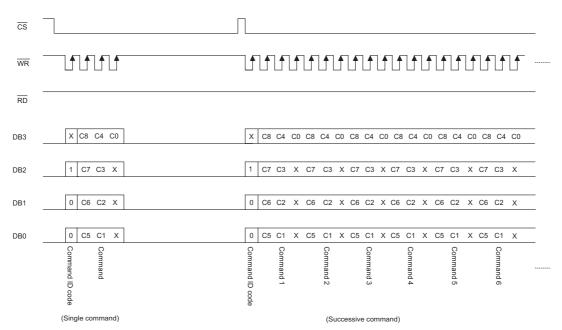

## **Timing Diagrams**

## READ mode (command ID code: 110)

## WRITE mode (command ID code: 101)

## READ-MODIFY-WRITE mode (command ID code: 101)

## Command mode (command ID code: 100)

Note: "X" stands for don't care

Rev. 1.30 13 November 10, 2005

## **Application Circuits**

## Host Controller with an HT1647 Display System

\*Note: The connection of  $\overline{\text{IRQ}}$  and  $\overline{\text{RD}}$  pin can be selected depending on the MCU.

The voltage applied to  $V_{LCD}$  pin must be lower than  $V_{DD}$ .

Adjust VR to fit LCD display, at V<sub>DD</sub>=5V, V<sub>LCD</sub>=4V, VR=15k $\Omega \pm 20\%$ .

It is recommended to select 1/5 bias to fit TN-type, STN-type LCDs and select 1/4 bias to fit ECB-type LCDs.

Adjust R (external pull high resistance) to fit user's time base clock.

## **Instruction Set Summary**

| Name                  | Command Code                            | D/C | Function                                                | Def. |

|-----------------------|-----------------------------------------|-----|---------------------------------------------------------|------|

| READ                  | A8 <b>110</b> -A7A6A5A4A3A2A1A0D3D2D1D0 | D   | Read data from the RAM                                  |      |

| WRITE                 | A8 <b>101</b> -A7A6A5A4A3A2A1A0D3D2D1D0 | D   | Write data to the RAM                                   |      |

| READ-MODIFY-<br>WRITE | A8 <b>101</b> -A7A6A5A4A3A2A1A0D3D2D1D0 | D   | D Read and Write data to the RAM                        |      |

| SYS DIS               | X100-0000-0000-XXXX                     | С   | C Turn Off both system oscillator and LCD bia generator |      |

| SYS EN                | X <b>100</b> -0000-0001-XXXX            | С   | Turn On system oscillator                               |      |

| LCD OFF               | X <b>100</b> -0000-0010-XXXX            | С   | Turn Off LCD display                                    | Yes  |

| LCD ON                | X <b>100</b> -0000-0011-XXXX            | С   | Turn On LCD display                                     |      |

| TIMER DIS             | X <b>100</b> -0000-0100-XXXX            | С   | Disable time base output                                | Yes  |

| WDT DIS               | X <b>100</b> -0000-0101-XXXX            | С   | Disable WDT time-out flag output                        | Yes  |

| TIMER EN              | X <b>100</b> -0000-0110-XXXX            | С   | C Enable time base output                               |      |

| WDT EN                | X <b>100</b> -0000-0111-XXXX            | С   | C Enable WDT time-out flag output                       |      |

| TONE OFF              | X <b>100</b> -0000-1000-XXXX            | С   | C Turn Off tone outputs                                 |      |

| CLR TIMER             | X <b>100</b> -0000-1101-XXXX            | С   | C Clear the contents of the time base generator         |      |

| CLR WDT               | X <b>100</b> -0000-1111-XXXX            | С   | C Clear the contents of the WDT stage                   |      |

| TONE 4K               | X <b>100</b> -0001-0000-XXXX            | С   | C Turn on tone output, tone frequency output 4kHz       |      |

| TONE 2K               | X100-0001-0001-XXXX                     | С   | Turn on tone output, tone frequency output: 2kHz        |      |

Rev. 1.30 14 November 10, 2005

| Name        | Command Code                          | D/C | Function                                                                                         | Def. |

|-------------|---------------------------------------|-----|--------------------------------------------------------------------------------------------------|------|

| IRQ DIS     | X100-0001-0010-XXXX                   | С   | Disable IRQ output                                                                               | Yes  |

| IRQ EN      | X <b>100</b> -0001-0011-XXXX          | С   | Enable IRQ output                                                                                |      |

| RC 32K      | X <b>100</b> -0001-0100-XXXX          | С   | System clock source, on-chip RC oscillator                                                       |      |

| EXT (XTAL)  | X <b>100</b> -0001-0101-XXXX          | С   | System clock source, external 32kHz clock source or crystal oscillator 32.768kHz                 |      |

| LARGE BIAS  | X <b>100</b> -0001-0110-XXXX          | С   | Large bias current option                                                                        | Yes  |

| MIDDLE BIAS | X <b>100</b> -0001-0111-XXXX          | С   | Middle bias current option                                                                       |      |

| SMALL BIAS  | X <b>100</b> -0001-1000-XXXX          | С   | Small bias current option                                                                        |      |

| BIAS 1/5    | X <b>100</b> -0001-1001-XXXX          | С   | LCD 1/5 bias option                                                                              | Yes  |

| BIAS 1/4    | X <b>100</b> -0001-1010-XXXX          | С   | LCD 1/4 bias option                                                                              |      |

| FRAME 170Hz | X100-0001-1100-XXXX                   | С   | Selects 170Hz frame frequency and activities segment signal width can be divided into 1 sections |      |

| FRAME 89Hz  | X <b>100</b> -0001-1101-XXXX          | С   | Selects 89Hz frame frequency and active segment signal width can be divided into 24 sections     |      |

| GRS LEVEL1  | X <b>100</b> -001 B4-B3 B2 B1 B0-XXXX | С   | Sets PWM data in gray scale level 1                                                              |      |

| GRS LEVEL2  | X <b>100</b> -010 B4-B3 B2 B1 B0-XXXX | С   | Sets PWM data in gray scale level 2                                                              |      |

| GRS LEVEL3  | X <b>100</b> -011 B4-B3 B2 B1 B0-XXXX | С   | Sets PWM data in gray scale level 3                                                              |      |

| GRS LEVEL4  | X <b>100</b> -100 B4-B3 B2 B1 B0-XXXX | С   | Sets PWM data in gray scale level 4                                                              |      |

| F1          | X <b>100</b> -1010-0000-XXXX          | С   | C Time base clock output: 1Hz The WDT time-out flag after: 4s                                    |      |

| F2          | X <b>100</b> -1010-0001-XXXX          | С   | C Time base clock output: 2Hz The WDT time-out flag after: 2s                                    |      |

| F4          | X <b>100</b> -1010-0010-XXXX          | С   | Time base clock output: 4Hz The WDT time-out flag after: 1s                                      |      |

| F8          | X <b>100</b> -1010-0011-XXXX          | С   | Time base clock output: 8Hz The WDT time-out flag after: 1/2s                                    |      |

| F16         | X <b>100</b> -1010-0100-XXXX          | С   | Time base clock output: 16Hz The WDT time-out flag after: 1/4s                                   |      |

| F32         | X <b>100</b> -1010-0101-XXXX          | С   | Time base clock output: 32Hz The WDT time-out flag after: 1/8s                                   |      |

| F64         | X <b>100</b> -1010-0110-XXXX          | С   | Time base clock output: 64Hz The WDT time-out flag after: 1/16s                                  |      |

| F128        | X <b>100</b> -1010-0111-XXXX          | С   | Time base clock output: 128Hz The WDT time-out flag after: 1/32s                                 |      |

| TEST        | X100-1111-1111-XXXX                   | С   | Test mode, user don't use.                                                                       |      |

| NORMAL      | X <b>100</b> -1111-1110-XXXX          | С   | Normal mode                                                                                      | Yes  |

Note: "X" stands for don't care

A8~A0: RAM address D3~D0: RAM data B4~B0: PWM data

D/C: Data/Command mode

Def.: Power-on reset default

All the bold forms, namely **110**, **101**, and **100**, are mode commands. Of these, **100** indicates the command mode ID. If successive commands have been issued, the command mode ID except for the first command will be omitted. The tone frequency source and the time base/WDT clock frequency source can be derived from an on-chip 32kHz RC oscillator, a 32.768kHz crystal oscillator, or an external 32kHz clock. Calculation of the frequency is based on the system frequency sources as stated above. It is recommended that the host controller should initialize the HT1647 after power-on reset, otherwise, power on reset may fail, which in turn leads to the malfunctioning of the HT1647.

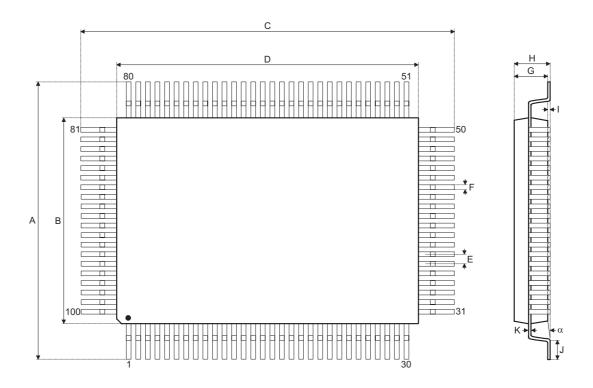

# **Package Information**

## 100-pin QFP (14×20) outline dimensions

| Cymrh al | Dimensions in mm |      |       |  |  |

|----------|------------------|------|-------|--|--|

| Symbol   | Min.             | Nom. | Max.  |  |  |

| А        | 18.80            | _    | 19.20 |  |  |

| В        | 13.90            | _    | 14.10 |  |  |

| С        | 24.80            | _    | 25.20 |  |  |

| D        | 19.90            | _    | 20.10 |  |  |

| E        | _                | 0.65 | _     |  |  |

| F        | _                | 0.30 | _     |  |  |

| G        | 2.50             | _    | 3.10  |  |  |

| Н        | _                | _    | 3.40  |  |  |

| 1        | _                | 0.10 | _     |  |  |

| J        | 1                | _    | 1.40  |  |  |

| K        | 0.10             | _    | 0.20  |  |  |

| α        | 0°               | _    | 7°    |  |  |

### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

## Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

### Holtek Semiconductor Inc. (Shanghai Sales Office)

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China 200233

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

## Holtek Semiconductor Inc. (Shenzhen Sales Office)

5/F, Unit A, Productivity Building, Cross of Science M 3rd Road and Gaoxin M 2nd Road, Science Park, Nanshan District,

Shenzhen, China 518057

Tel: 0755-8616-9908, 8616-9308

Fax: 0755-8616-9533

### Holtek Semiconductor Inc. (Beijing Sales Office)

Suite 1721, Jinyu Tower, A129 West Xuan Wu Men Street, Xicheng District, Beijing, China 100031

Tel: 010-6641-0030, 6641-7751, 6641-7752

Fax: 010-6641-0125

## Holtek Semiconductor Inc. (Chengdu Sales Office)

709, Building 3, Champagne Plaza, No.97 Dongda Street, Chengdu, Sichuan, China 610016

Tel: 028-6653-6590 Fax: 028-6653-6591

## Holmate Semiconductor, Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

### Copyright © 2005 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.30 November 10, 2005