NT7450B

### **Features**

- Fast 8-bit MPU interface compatible with 80-and 68-family microcomputers

- Many command set

- Total 80 (segment + common) drive sets

- Low power 30  $\mu$  W at 2 kHz external clock

- Wide range of supply voltages

■ VDD-Vss: +2.7~+5.5V VDD-V5: +3.5~+13.0V

Low-power CMOS

### **Descriptions**

The NT7450B family of dot matrix LCD drivers is designed for the display of characters and graphics. The drivers generate LCD drive signals derived from bit mapped data stored in an internal RAM. The drivers are available in two configurations. The NT7450B family drivers incorporate innovative circuit design strategies to achieve very low power dissipation at a wide range of operating voltages.

These features give the designer a flexible means of implementing small to medium size LCD displays for compact, low power systems.

The NT7450B which is able to drive two lines of twelve characters each.

### **Order Information**

# NT7450B

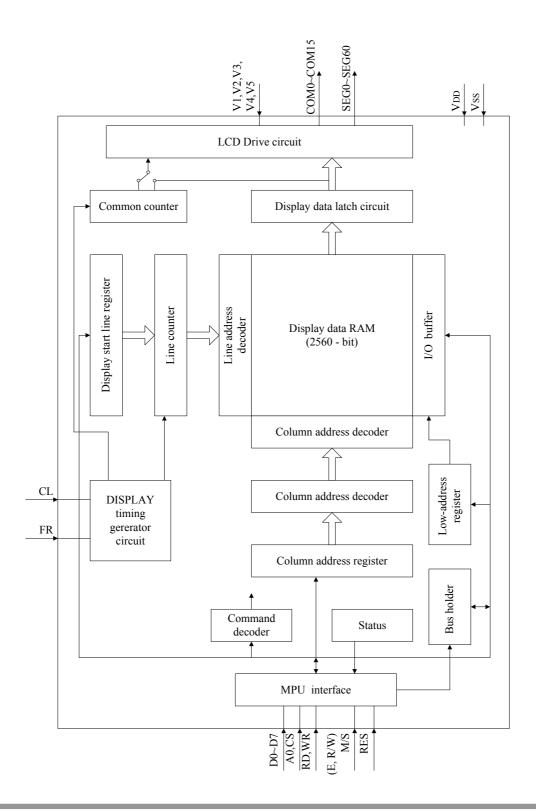

## **BOLCK DIAGRAM**

NT7450B

## **PIN DESCRIPTION**

#### **Power Pins**

| Name                                         | Description                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| VDD                                          | Connected to the +5V dc power. Common to the Vcc MPU power pin.                                                                                                                                                                                                          |  |  |  |  |  |  |

| VSS 0Vdc pin connected to the system ground. |                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

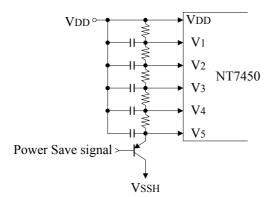

|                                              | Multi-level power supplies for LCD driving. The voltage determined for each liquid crystal cell is divided by resistance or it is converted in impedance by the op amp and supplied. These voltages must satisfy the following: $VDD \ge V1 \ge V2 \ge V3 \ge V4 \ge V5$ |  |  |  |  |  |  |

#### **System Bus Connection Pins**

| Name     | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7 to D0 | Three-state I/O. The 8-bit bi-directional data buses to be connected to the 8- or 16-bit standard MPU data buses.                                                                                                                                                                                                                                                                                     |

| Α0       | Input. Usually connected to the low-order bit of the MPU address bus and used to identify the data or a command. A0=0: D0 to D7 are display control data. A0=1: D0 to D7 are display data.                                                                                                                                                                                                            |

| RES      | Input.  When the RES signal goes                                                                                                                                                                                                                                                                                                                                                                      |

| cs       | Input. Active low. Effective for an external clock operation model only.  An address bus signal is usually decoded by use of chip select signal, and it is entered. If the system has a built-in oscillator, this is used as an input pin to the oscillator amp and a Rf oscillator resistor is connected to it. In such case, the RD, WR and E signals must be ORed with the CS signals and entered. |

| E(RD)    | If the 68-series MPU is connected: Input. Active high. Used as an enable clock input of the 68-series MPU. If the 80-series MPU is connected: Input. Active low. The RD signal of the 80series MPU is entered in this pin. When this signal is kept low, the NT7450B data bus is in the output status.                                                                                                |

| R/W(WR)  | If the 68-series MPU is connected: Input. Used as input pins of read control signals (if R/W is high) or writes control signals (if low). If the 80-series MPU is connected: Input. Active low. The WR signal of the 80-series MPU is entered in this pin. A signal on the data bus is fetched at the rising edge of WR signal.                                                                       |

# NT7450B

#### **LCD Drive Circuit Signals**

| Name | Description                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| CL   | Input.  Effective for an external clock operation model only.  This is a display data latch signal to count up the line counter and common counter at each signal falling and rising edges. If the system has a built-in oscillator. This is used as an output pin for the oscillator amp and a Rf oscillator resistor is connected to it. |  |  |  |  |  |  |  |  |  |  |

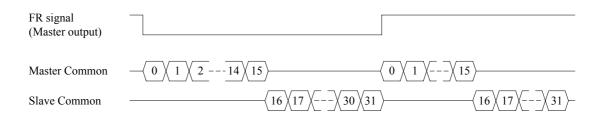

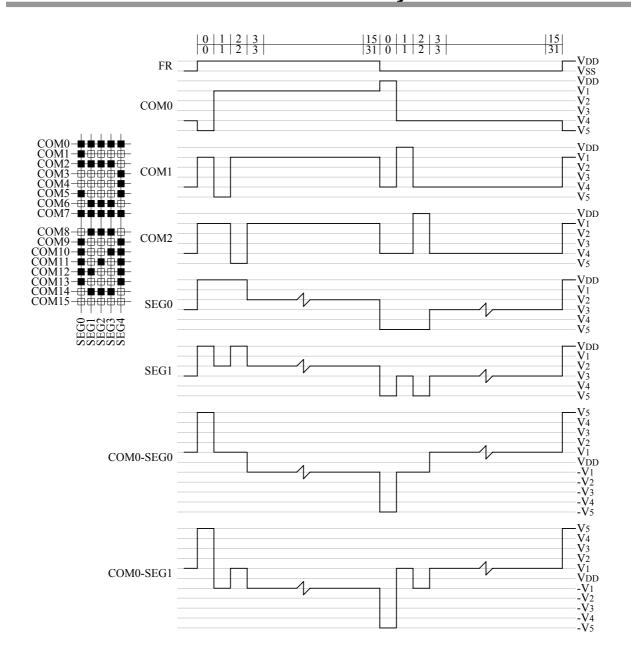

| FR   | Input/output. This is an I/O pin of LCD AC signals, and connected to the M terminal of common driver. I/O selection Common oscillator built-in model: Output if M/S is 1; Input if M/S is 0 Dedicate segment model: Input                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| SEGn | Output. The output pin for LCD column (segment) driving. A single level of VDD, V2, V3 and V5 is selected by the combination of display RAM contents and FR signal.  FR signal  Count output level  VDD V2 V5 V3  V3                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| COMn | Output. The Output pin for LCD common (Low) driving. A single level of VDD, V1, V4 and V5 is selected by the combination of common counter output and FR signal. The slave LSI has the reverse common output scan sequence than the master LSI.  FR signal  Count output  V5 V1 VDD V4  level  V4                                          |  |  |  |  |  |  |  |  |  |  |

|      | Input. The master LSI or slave LSI operation select pin for the NT7450B. Connected to VDD (to select the master LSI operation mode) or Vss (to select the slave LSI operation mode). When this M/S pin is set, the functions of FR, COM0 to COM15, OSC1 (CS), and OSC2                                                                     |  |  |  |  |  |  |  |  |  |  |

NT7450B

#### **BLOCK DESCRIPTION**

#### **System Bus**

#### **MPU** interface

Selecting an interface type

The NT7450B series transfers data via 8-bit bi-directional data buses (D0 to D7). As its Reset pin has the MPU interface select function, the 80-series MPU or the 68-series MPU can directly be connected to the MPU bus by the selection of high or low RES signal level after reset (see Table 1).

When the  $\overline{\text{CS}}$  signal is high, the NT7450B series is disconnected from the MPU bus and set to stand by. However, the reset signal is entered regardless of the internal setup status.

Table 1

| RES signal input level | MPU type  | A0 | Е  | R/W      | CS | D0 to D7 |

|------------------------|-----------|----|----|----------|----|----------|

| Active low             | 68-series | 1  | 1  | <b>↑</b> | 1  | <b>↑</b> |

| Active High            | 80-series | 1  | RD | WR       | 1  | 1        |

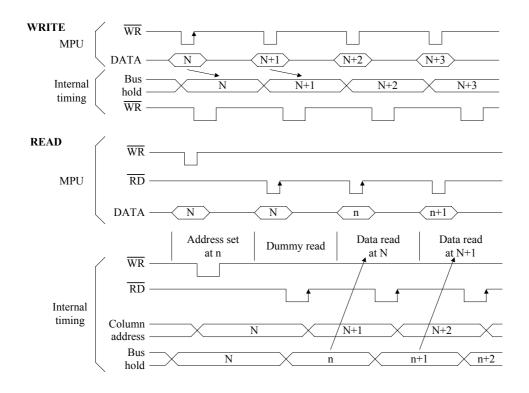

#### **Data transfer**

The NT7450B and NT7451B divers use the A0, E (or RD) and R/W (or WR) signals to transfer data between the system MPU and internal registers. The combinations used are given in the table blow.

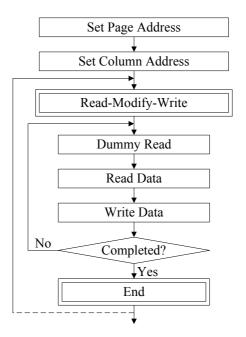

In order to match the timing requirements of the MPU with those of the display data RAM and control registers all data is latched into and out of the driver. This introduces a one cycle delay between a read request for data and the data arriving. For example when the MPU executes a read cycle to access display RAM the current contents of the latch are placed on the system data bus while the desired contents of the display RAM are moved into the latch.

This means that a dummy read cycle has to be executed at the start of every series of reads. See Figure 1.

No dummy cycle is required at the start of a series of writes as data is transferred automatically from the input latch to its destination.

| Common | 68 MPU | 80 N | /IPU                              |                                      |  |  |  |  |

|--------|--------|------|-----------------------------------|--------------------------------------|--|--|--|--|

| Α0     | R/W    | RD   | $\overline{\mathbf{W}}\mathbf{R}$ | Function                             |  |  |  |  |

| 1      | 1      | 0    | 1                                 | Read display data                    |  |  |  |  |

| 1      | 0      | 1    | 0                                 | Write display data                   |  |  |  |  |

| 0      | 1      | 0    | 1                                 | Read status                          |  |  |  |  |

| 0      | 0      | 1    | 0                                 | Write to internal register (command) |  |  |  |  |

NT7450B

Figure 1 Bus Buffer Delay

#### **Busy flag**

When the Busy flag is logical 1, the NT7450B series is executing its internal operations. Any command other than Status Read is rejected during this time. The Busy flag is output at pin D7 by the Status Read command. If an appropriate cycle time (tcyc) is given, this flag needs not be checked at the beginning of each command and therefore, the MPU processing capacity can greatly be enhanced.

#### **Display Start Line and Line Count Registers**

The contents of this register form a pointer to a line of data in display data RAM corresponding to the first line of the display (COM0), and are set by the Display Start Line command.

The contents of the display start line register are copied into the line count register at the start of every frame that is on each edge of FR. The line count register is incremented by the CL clock once for every display line, thus generating a pointer to the current line of data, in display data RAM, being transferred to the segment driver circuits.

#### **Column Address Counter**

The column address counter is a 7-bit preset table counter that supplies the column address for MPU access to the display data RAM. See figure 2. The counter is incremented by one every time the driver receives a Read or Write Display Data command. Addresses above 50H are invalid, and the counter will not increment past this value. The contents of the column address counter are set with the Set Column Address command.

NT7450B

#### Page Register

The page resister is a 2-bit register that supplies the page address for MPU access to the display data RAM. See Figure 2. The contents of the page register are set by the Set Page Register command.

#### **Display Data RAM**

The display data RAM stores the LCD display data, on a 1-bit per pixel basis. The relation-ship between display data, display address and the display is shown in Figure 2.

#### **Common Timing Generator Circuit**

Generates common timing signals and FR frame signals from the CL basic clock. The 1/16 or 1/32 duty (forNT7450B) can be selected by the Duty Select command. If the 1/32 duty is selected for the NT7450B, the 1/32 duty is provided by two chips, COM1~16 by the master and COM17~32 by the slave chips in the common

multi-chip mode.

#### Display Data Latch Circuit

This latch stores one line of display data for use by the LCD driver interface circuitry. The output of this latch is controlled by the Display ON/OFF and Static Drive ON/OFF commands.

#### **LCD Driver Circuit**

The LCD driver circuitry generates the 80-4-level signals used to drive the LCD panel, using output from the display data latch and the common timing generator circuitry.

#### **Display Timing Generator**

This circuit generates the internal display- timing signal using the basic clock, CL, and the frame signals, FR.

FR is used to generate the dual frame AC-drive wave-from (type B drive) and to lock the line counter and common timing generator to the system frame rate.

CL is used to lock the line counter to the system line scan rate. If a system uses both NT7450Bs and NT7451s they must have the same CL frequency rating.

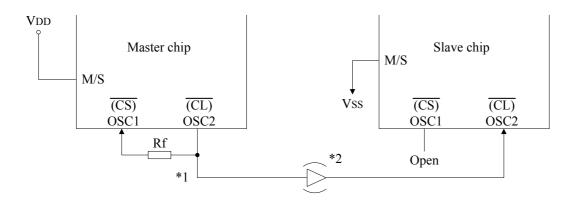

#### Oscillator Circuit (NT7450B<sub>OA</sub>)

A low power-consumption CR oscillator for adjusting the oscillation frequency is using Rf oscillation resistor only. This circuit generates a display timing signal. Some of NT7450B series models have a built-in oscillator and others use an external clock. This difference must be checked before use.

Connect the Rf oscillation resistor as follows. To suppress the built-in oscillator circuit and drive the MPU using an external clock, the clock having the same phase as the OSC2 of mater chip into OSC2 of the slave chip. MPU having a built-in oscillator

## NT7450B

\*1 If the parasitic capacitance of this section increases, the oscillation frequency may shift to the lower frequency. Therefore, the Rf oscillation frequency must be reduced below the specified level.

\*2 A CMOS buffer is required if the oscillation circuit is connected to two or more slave chips.

#### **Reset Circuit**

Detects a rising or falling edge of a RES input and initializes the MPU during power-on.

· Initialization status

Display is off.

Display start line register is set to line 1.

Static drive is turned off.

Column address counter is set to address 0.

Page address register is set to page 3.

1/32 duty NT7450B is selected.

Forward ADC is selected (ADC command D0 is 0 and ADC status flag is 1).

Read-modify-write is turned off.

The input signal level at RES pin is sensed, and an MPU interface mode is selected as shown on Table 1. For the 80-series MPU, the RES input is passed through the inverter and the active high reset signal must be entered. For the 68-series MPU, the active low reset signal must be entered.

As shown for the MPU interface (reference example), the RES pin must be connected to the Reset pin and reset at the same time as the MPU initialization.

If the MPU is not initialized by the use of  $\overline{\text{RES}}$  pin during power-on, an unrecoverable MPU failure may occur. When the Reset command id issued, initialization.

# NT7450B

Figure 2 Display Data RAM Addressung Page address D1,D2=0,0 0,1 1,1 1,0 Column address D6 D4 D6 D4 D6 D 4 D D1 D2 DO D3D D1 D D6 D5 D4 D3ADC D5 D2 D0 SEG pin D0=1 D0=0 00H 4FH 0 4EH 01H 2 4DH 02H 4CH 03H 4 4BH 04H 05H 5 4AH 6 49H 06H 48H 07H Page2 77 02H 4DH 01H 4EH 79 4FH 00H Line address 0CH 09H 0AH 0DH 05H 06H 07H 0EH 10H04H 18H 16H 14H 12H Display area Start line (Example) Response 1/16 Common output COM 0 COM 25 COM 26 COM 27 COM 28 COM 29 COM 30 COM 21 COM 22 COM 23 COM 24 COM 15 COM 16 COM 17 COM 18 COM 19 COM 9 COM 10 COM 11 COM 12 COM 13 COM 20 COM 5 COM 6 COM 7 COM 8 COM 3 COM 1

# NT7450B

NT7450B

#### **COMMANDS**

#### **Summary**

| Commond                            | Code |    |                                   |      |     |                                   |       |           |      | Function |                                                          |                                                                                                                                                     |

|------------------------------------|------|----|-----------------------------------|------|-----|-----------------------------------|-------|-----------|------|----------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                            | A0   | RD | $\overline{\mathbf{W}\mathbf{R}}$ | D7   | D6  | D5                                | D4    | D3        | D2   | D1       | D0                                                       | Function                                                                                                                                            |

| Display<br>On/Off                  | 0    | 1  | 0                                 | 1    | 0   | 1                                 | 0     |           |      |          | 0/1                                                      | Turns display on or off.<br>1: ON, 0: OFF                                                                                                           |

| Display start line                 | 0    | 1  | 0                                 | 1    | 1   | 0 Display start address (0 to 31) |       |           |      | ess      | Specifies RAM line corresponding to top line of display. |                                                                                                                                                     |

| Set page address                   | 0    | 1  | 0                                 | 1    | 0   | 1                                 | 1     | 1         | 0    |          | ige<br>o 3)                                              | Sets display RAM page in page address register.                                                                                                     |

| Set column<br>(Segment)<br>address | 0    | 1  | 0                                 | 0    | (   | Colur                             | nn ad | ddres     | s (0 | to 79    | )                                                        | Sets Display RAM column address in column address register.                                                                                         |

| Read status                        | 0    | 0  | 1                                 | BUSY | ADC | ON/OFF                            | RESET | 0         | 0    | 0        | 0                                                        | Reads the following status: BUSY 1: Busy 0: Ready ADC 1: CW output 0: CCW output NO/OFF 1: Display off 0: Display on RESET 1: Being reset 0: Normal |

| Write display data                 | 1    | 1  | 0                                 |      |     | ,                                 | Write | data      | ì    |          |                                                          | Writes data from data bus into display RAM.                                                                                                         |

| Read display data                  | 1    | 0  | 1                                 |      |     | 1                                 | Read  | data      | ì    |          |                                                          | Reads data from display RAM onto data bus.                                                                                                          |

| Select ADC                         | 0    | 1  | 0                                 | 1    | 0   | 1                                 | 0     | 0         | 0    | 0        | 0/1                                                      | 0:CW output, 1:CCW output                                                                                                                           |

| Static drive<br>ON/OFF             | 0    | 1  | 0                                 | 1    | 0   | 1                                 | 0     | 0         | 1    | 0        | 0/1                                                      | Selects static driving operation. 1:Static drive, 0:Normal driving                                                                                  |

| Select duty                        | 0    | 1  | 0                                 | 1    | 0   | 1                                 | 0     | 1 0 0 0/1 |      |          | 0/1                                                      | Selects LCD duty cycle 1:1/32, 0:1/16                                                                                                               |

| Read-Modify-<br>Write              | 0    | 1  | 0                                 | 1    | 1   | 1                                 | 0     | 0         | 0    | 0        | 0                                                        | Read-modify-write ON                                                                                                                                |

| End                                | 0    | 1  | 0                                 | 1    | 1   | 1                                 | 0     | 1         | 1    | 1        | 0                                                        | Read-modify-write OFF                                                                                                                               |

| Reset                              | 0    | 1  | 0                                 | 1    | 1   | 1                                 | 0     | 0         | 0    | 1        | 0                                                        | Software reset                                                                                                                                      |

#### **Command Description**

Table 3 is the command table. The NT7450B series identifies a data bus using a combination of A0 and  $\overline{R/W}$  ( $\overline{RD}$  or  $\overline{WR}$ ) signals. As the MPU translates a command in the internal timing only (independent from the external clock), its speed is very high. The busy check is usually not required.

#### **Display ON/OFF**

| A0 | RD | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |         |

|----|----|----------------------------------------|----|----|----|----|----|----|----|----|---------|

| 0  | 0  | 0                                      | 1  | 0  | 1  | 0  | 1  | 1  | 1  | D  | AEH, AF |

This command turns the display on and off.

D=1: Display OND=0: Display OFF

NT7450B

#### **Display Start Line**

This command specifies the line address shown in Figure 2 and indicates the display line that corresponds to COMO. The display area begins at the specified line address and continues in the line address increment direction. This area having the number of lines of the specified display duty is displayed. If the line address is changed dynamically by this command, the vertical smooth scrolling and paging can be used.

| A0 | $\overline{\mathrm{RD}}$ | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |          |

|----|--------------------------|----------------------------------------|----|----|----|----|----|----|----|----|----------|

| 0  | 1                        | 0                                      | 1  | 1  | 0  | A4 | A3 | A2 | A1 | A0 | C0H, DFH |

This command loads the display start line register.

| A4 | A3 | A2 | A1 | A0 | Line Address |

|----|----|----|----|----|--------------|

| 0  | 0  | 0  | 0  | 0  | 0            |

| 0  | 0  | 0  | 0  | 1  | 1            |

|    |    |    |    |    |              |

|    |    |    |    |    |              |

|    |    |    |    |    | •            |

|    |    | :  |    |    | · .          |

| 1  | 1  | 1  | 1  | 1  | 31           |

See Figure 2.

#### **Set Page Address**

This command specifies the page address that corresponds to the low address of the display data RAM when it is accessed by the MPU. Any bit of the display data RAM can be accessed when its page address and column address are specified. The display status is not changed even when the page address is changed.

| A0 | $\overline{\text{RD}}$ | R/W<br>WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |          |

|----|------------------------|-----------|----|----|----|----|----|----|----|----|----------|

| 0  | 1                      | 0         | 1  | 0  | 1  | 1  | 1  | 0  | A1 | A0 | B8H, BBH |

This command loads the page address register.

| A1 | A0 | Page |

|----|----|------|

| 0  | 0  | 0    |

| 0  | 1  | 1    |

| 1  | 0  | 2    |

| 1  | 1  | 3    |

See Figure 2.

#### **Set Column Address**

This command specifies a column address of the display data RAM. When the display data RAM is accessed by the MPU continuously, the column address is incremented by 1 each time it is accessed from the set address. Therefore, the MPU can access to data continuously. The column address stops to be incremented at address 80 and the page address is not changed continuously.

| A0 | RD | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |            |

|----|----|----------------------------------------|----|----|----|----|----|----|----|----|------------|

| 0  | 1  | 0                                      | 0  | A6 | A5 | A4 | A3 | A2 | A1 | A0 | 00H to 4FH |

NT7450B

This command loads the column address register.

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | Line Address |

|----|----|----|----|----|----|----|--------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0            |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1            |

|    |    |    |    |    |    |    |              |

|    |    |    |    |    |    |    |              |

|    |    |    |    |    |    |    |              |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 79           |

#### **Read Status**

| A0 | $\overline{\mathrm{RD}}$ | $\frac{R/\overline{W}}{WR}$ | D7   | D6  | D5      | D4    | D3 | D2 | D1 | D0 |

|----|--------------------------|-----------------------------|------|-----|---------|-------|----|----|----|----|

| 0  | 0                        | 1                           | Busy | ADC | On/ Off | Reset | 0  | 0  | 0  | 0  |

Reading the command I/O register (A0=0) yields system status information.

• The busy bit indicates whether the driver will accept a command or not.

Busy=1: The driver is currently executing a command or is resetting. No new command will be accepted.

Busy=0: The driver will accept a new command.

• The ADC bit indicates the way column addresses are assigned to segment drivers.

ADC=1: Normal. Column address  $n \rightarrow$  segment driver n.

ADC=0: Inverted. Column address 79-u → segment driver u.

• The ON/OFF bit indicates the current status of the display.

It is the inverse of the polarity of the display ON/OFF command.

ON/OFF=1: Display OFF ON/OFF=0: Display ON

• The RESET bit indicates whether the driver is executing a hardware or software reset or if it is in normal operation mode.

RESET=1: Currently executing reset command.

RESET=0: Normal operation

#### **Write Display Data**

| A0 | RD | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4    | D3   | D2 | D1 | D0 |

|----|----|----------------------------------------|----|----|----|-------|------|----|----|----|

| 1  | 1  | 0                                      |    |    |    | Write | data |    |    |    |

Write 8-bits of data into the display data RAM, at a location specified by the contents of the column address and page, address registers and then increments the column address register by one.

#### **Read Display Data**

| Ī |    |                        | $R/\overline{W}$         |    |    |    |      |      |    |    |    |

|---|----|------------------------|--------------------------|----|----|----|------|------|----|----|----|

|   | A0 | $\overline{\text{RD}}$ | $\overline{\mathrm{WR}}$ | D7 | D6 | D5 | D4   | D3   | D2 | D1 | D0 |

| Ī | 1  | 0                      | 1                        |    |    |    | Read | data |    |    |    |

Reads 8-bit of data from the data I/O latch, updates the contents of the I/O latch with display data from the display data RAM location specified by the contents of the column address and page address registers and then increments the column address register.

NT7450B

After loading a new address into the column address register one dummy read is required before valid data is obtained.

#### **Select ADC**

| A0 | RD | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |   |

|----|----|----------------------------------------|----|----|----|----|----|----|----|----|---|

| 0  | 1  | 0                                      | 1  | 0  | 1  | 0  | 0  | 0  | 0  | D  | Α |

A0H, A1H

This command selects the relationship between display data RAM column addresses and segment drivers.

D=1: SEG0 ← column address 4FH, ...(Inverted)

D=0: SEG0 ← column address 00H, ...(Normal)

This command is provided to reduce restrictions on the placement of driver ICs and routing of traces during printed circuit board design. See Figure 2 for a table of segments and column addresses for the two values of D

#### Static Drive ON/OFF

| A0 | RD | $\frac{R/\overline{W}}{WR}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |          |

|----|----|-----------------------------|----|----|----|----|----|----|----|----|----------|

| 0  | 1  | 0                           | 1  | 0  | 1  | 0  | 0  | 1  | 0  | D  | A4H, A5H |

Forces display on and all common outputs to be selected.

D=1: Static drive on D=0: Static drive off

#### **Select Duty**

| A0 | RD | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----------------------------------------|----|----|----|----|----|----|----|----|

| 0  | 1  | 0                                      | 1  | 0  | 1  | 0  | 1  | 0  | 0  | D  |

A8H, A9H

This command sets the duty cycle of the LCD drive and is only valid for the NT7450B. It is invalid for the NT7451 whose performs passive operation. The duty cycle of the NT7451 is determined by the externally generated FR signal.

D=1: 1/32 duty cycle D=0: 1/16 duty cycle

When using the NT7450BOA, (having a built-in oscillator) and the NT7451OA continuously, set the duty as follows:

| NT7450BOA | NT7451OA |

|-----------|----------|

| 1/32      | 1/32     |

| 1/16      | 1/16     |

#### Read-Modify-Write

| A0 | RD | $\frac{R/\overline{W}}{WR}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |

|----|----|-----------------------------|----|----|----|----|----|----|----|----|-----|

| 0  | 1  | 0                           | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | E0H |

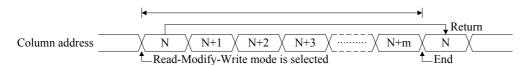

This command defeats column address register auto-increment after data reads. The current contents of the column address register are saved. This mode remains active until an End command is received.

Operation sequence during cursor display

NT7450B

When the End command is entered, the column address is returned to the one used during input of Read-Modify-Write command. This Function can reduce the load of MPU when data change is repeated at a specific display area (such as cursor blinking).

\* Any command other than Data Read or Write can be used in the Read-Modify-Write mode. However, the Column Address Set command cannot be used.

#### End

| A0 | $\overline{\mathrm{RD}}$ | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |

|----|--------------------------|----------------------------------------|----|----|----|----|----|----|----|----|-----|

| 0  | 1                        | 0                                      | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | EEH |

This command cancels read-modify-write mode and restores the contents of the column address register to

their value prior to the receipt of the Read-Modify-Write command.

#### Reset

| A0 | $\overline{\text{RD}}$ | $\frac{R/\overline{W}}{\overline{W}R}$ | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |

|----|------------------------|----------------------------------------|----|----|----|----|----|----|----|----|-----|

| 0  | 1                      | 0                                      | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | E2H |

#### This command clears

- · the display start line register.

- and set page address register to 3 page.

It does not affect the contents of the display data RAM.

NT7450B

When the power supply is turned on, a Reset signal is entered in the RES pin. The Reset command cannot be used instead of this Reset signal.

#### **Power Save (Combination command)**

The Power Save mode is selected if the static drive is turned ON when the display is OFF. The current consumption can be reduced to almost the static current level. In the Power Save mode:

- (a) The LCD drive is stopped, and the segment and common driver outputs are set to the VDD level.

- (b) The external oscillation clock input is inhibited, and the OSC2 is set to the floating mode.

- (c) The display and operation modes are kept.

The Power Save mode is released when the display is turned ON or when the static drive is turned OFF. If the LCD drive voltage is supplied from an external resistance divider circuit, the current passing through this resistor must be cut by the Power Save signal.

If the LCD drive-power generated by resistance division, the resistance and capacitance are determined by the LCD panel size. After the panel size has been determined, reduce the resistance to the level where the display quality is not affected and reduce the power consumption using the divider resistor.

## NT7450B

### **SPECIFICATIONS**

#### **Absolute Maximum Ratings**

| Parameter                          | Symbol      | Rating          | Unit                   |

|------------------------------------|-------------|-----------------|------------------------|

| Supply voltage(1)                  | Vss         | -8.0 to +0.3    | V                      |

| Supply voltage(2)                  | V5          | -16.5 to +0.3   | V                      |

| Supply voltage(3)                  | V1,V4,V2,V3 | V5 to +0.3      | V                      |

| Input voltage                      | VIN         | Vss-0.3 to +0.3 | V                      |

| Output voltage                     | VO          | Vss-0.3 to +0.3 | V                      |

| Power dissipation                  | PD          | 250             | mW                     |

| Operating temperature              | Topr        | -40 to +85      | $^{\circ}\!\mathbb{C}$ |

| Storage temperature                | Tstg        | -65 to +150     | $^{\circ}\!\mathbb{C}$ |

| Soldering temperature time at lead | Tsol        | 260, 10         | ℃, sec                 |

Notes:

All voltages are specified relative to VDD=0V.

The following relation must be always hold

$VDD \!\! \ge \! V1 \!\! \ge \!\! V2 \!\! \ge \!\! V3 \!\! \ge \!\! V4 \!\! \ge \!\! V5$

Exceeding the absolute maximum ratings may cause permanent damage to the device. Functional operation under these conditions is not implied.

The soldering process can reduce moisture resistance of flat packages, so care should be taken to avoid thermally stressing the package during board assembly.

#### **Electrical Specifications**

#### **DC Characteristics**

Ta=-20 to 75°C, VDD=0V unless stated otherwise

| Par                       | ameter                     | Symbol   | Con         | dition       |          | Ratin | g        | Unit  | Applicable Pin         |  |

|---------------------------|----------------------------|----------|-------------|--------------|----------|-------|----------|-------|------------------------|--|

| Para                      | airietei                   | Syllibol | Con         | uition       | Min.     | Тур.  | Max.     | Ullit | Applicable Fill        |  |

| Operating v note1. Reco   | oltage (1) See<br>ommended | VSS      |             |              | -5.5     | -     | -2.7     | V     | VSS                    |  |

| Operating                 | Recommend ed               | V5       |             |              | -13.0    | -     | -3.5     | V     | V5 See note 10         |  |

|                           | Allowable                  |          |             |              | -13.0    | -     | -        |       |                        |  |

| voltage (2)               | Allowable                  | V1, V2   |             |              | 0.6xV5   | -     | VDD      | V     | V1, V2                 |  |

|                           | Allowable                  | V3, V4   |             |              | V5       | -     | 0.4xV5   | V     | V3, V4                 |  |

|                           | ·                          |          |             |              | VSS+2.0  | -     | VDD      |       | See note 2 & 3         |  |

| High lovel in             | nput voltage               | VIHC     |             |              | 0.2x VSS | -     | VDD      |       | See note 2 & 3         |  |

| High-level II             | iput voitage               | VIHT     | VSS         | S=-3V        | 0.2x VSS | -     | VDD      |       | See note 2 & 3         |  |

|                           |                            | VIHC     | VSS         | S=-3V        | 0.2x VSS | -     | VDD      | V     | See note 2 & 3         |  |

|                           |                            | VILT     |             |              | VSS      |       | VSS+0.8  | V     | See note 2 & 3         |  |

| l ovy lovel in            | put voltage                | VILC     |             |              | VSS      |       | 0.8xVSS  |       | See Hote 2 & 3         |  |

| Low-level II              | iput voitage               | VILT     | VSS=-3V     |              | VSS      |       | 0.85xVSS |       | See note 2 & 3         |  |

|                           |                            | VILC     | VSS         | S=-3V        | VSS      |       | 0.8xVSS  |       | See note 2 & 3         |  |

|                           |                            | VOHT     | IOH:        | =-3mA        | VSS+2.4  | -     | -        |       | 0000                   |  |

|                           |                            | VOHC1    | IOH:        | =-2mA        | VSS+2.4  | -     | -        | V     | OSC2                   |  |

|                           |                            | VOHC2    | IOH=        | -120 μ A     | 0.2x VSS | -     | -        |       | See note 4 & 5         |  |

| High-level output voltage |                            | VOHT     | VSS=-3<br>V | IOH=-2m<br>A | 0.2x VSS |       |          |       |                        |  |

|                           |                            | VOHC1    | VSS=-3<br>V | IOH=-2m<br>A | 0.2x VSS |       |          | V     | OSC2<br>See note 4 & 5 |  |

|                           |                            | VOHC2    | VSS=-3<br>V | IOH=-2m<br>A | 0.2x VSS |       |          |       |                        |  |

# NT7450B

#### DC Characteristics (Cont'd)

Ta=-20 to 75°C, VDD=0V unless stated otherwise

| D 4                        | 0      | 0!'                                                                  | 42             |      | Ratin |         |                  | A saa li sa la la Disa  |  |

|----------------------------|--------|----------------------------------------------------------------------|----------------|------|-------|---------|------------------|-------------------------|--|

| Parameter                  | Symbol | Condi                                                                | tion           | Min. | Тур.  | Max.    | Unit             | Applicable Pin          |  |

| Low-level output voltage   | VOLT   | IOL=3.                                                               | 0mA            |      |       | VSS+0.4 | ٧                | OSC2                    |  |

|                            | VOLC1  | IOL=2.                                                               |                |      |       | VSS+0.4 | V                | See note 4 & 5          |  |

|                            | VOLC2  | IOL=12                                                               | 0 μ <b>A</b>   |      |       | 0.8xVSS |                  |                         |  |

|                            | VOLT   | VSS=-3V                                                              | IOH=-2mA       |      |       | 0.8xVSS |                  | OSC2                    |  |

|                            | VOLC1  | VSS=-3V                                                              | IOH=-2mA       |      |       | 0.8xVSS | V                | See note 4 & 5          |  |

|                            | VOLC2  | VSS=-3V                                                              | IOH=-2 μ A     |      |       | 0.8xVSS |                  | OCC HOIC 4 Q 3          |  |

| Input leakage<br>current   | ILI    |                                                                      |                | -1.0 |       | 1.0     | $\mu$ A          | See note 6              |  |

| Output leakage current     | ILO    |                                                                      |                | -3.0 |       | 3.0     | $\mu$ A          | See note 7              |  |

| LCD drive ON               |        |                                                                      | V5=-5.0        |      | 5.0   | 7.5     |                  | SEG0~79                 |  |

| resister                   | RON    | Ta=25°ℂ                                                              | V5=-3.5        |      | 10.0  | 50.0    | ΚΩ               | COM0~15, See<br>note 11 |  |

| Static current dissipation | IDDQ   | CS=CL=VDD                                                            |                |      | 0.05  | 1.0     | $\mu$ A          | VDD                     |  |

|                            | IDD(1) | During display                                                       | fCL= 2KHz      |      | 2.0   | 5.0     | $\mu$ A          | VDD<br>See note 12 & 13 |  |

|                            |        | V5=-5.0V                                                             | Rf=1M $\Omega$ |      | 9.5   | 15.0    | μπ               | & 14                    |  |

| Dynamic current            |        | During display<br>V5=-5.0V                                           | fCL= 2KHz      |      | 1.5   | 4.5     | $\mu$ A          | VDD                     |  |

| dissipation                |        | VSS=-3V                                                              | Rf=1M $\Omega$ |      | 6.0   | 12.0    | $\mu$ A          | See note 12 & 13        |  |

|                            |        | During access t                                                      |                |      | 300   | 500     |                  |                         |  |

|                            | IDD(2) | VSS=<br>During access t                                              | • •            |      | 150   | 300     | $\mu \mathbf{A}$ | See note 8              |  |

| Input pin capacitance      | CIN    | Ta=25°ℂ,                                                             |                |      | 5.0   | 8.0     | pF               | All input pins          |  |

| Oscillation                | fOSC   | Rf=1M $\Omega$ ±2%,<br>VSS=-5.0V<br>Rf=1M $\Omega$ ±2%,<br>VSS=-3.0V |                | 15   | 18    | 21      | KHz              | See note 9              |  |

| frequency                  | 1030   |                                                                      |                | 11   | 16    | 21      | r\⊓Z             | See note 9              |  |

| Reset time                 | tR     |                                                                      |                | 1.0  |       |         | μs               | RES<br>See note 15      |  |

#### Notes:

- 1. Operation over the specified voltage range is guaranteed, except where the supply voltage changes suddenly during CPU access.

- 2. A0, D0 to D7, E(or RD), R/W (or WR) and CS

- 3. CL, FR, M/S and RES

- 4. D0 to D7

- 5. FR

- 6. A0, E (or RD), R/W (or WR), CS, CL, M/S and RES

- 7. When D0 to D7 and FR are high impedance.

- 8. During continual write access frequency.

- 9. See figure below for details

- 10. See figure below for details

- 11. For a voltage differential of 0.1 V between input (V1,..., V4) and output (COM, SEG) pins. All voltages within specified operating voltage range.

- 12. NT7450B and NT7451 only. Does not include transient currents due to stray and panel capacitances.

NT7450B

- 13. NT7450B only. Does not include transient currents due to stray and panel capacitances.

- 14. NT7451 only. Does not include transient currents due to stray and panel capacitances.

- 15.tR (Rest time) represents the time from the RES signal edge to the completion of rest of the internal circuit. Therefore, the NT7450B series enters the normal operation status after this tR.

#### **AC Characteristics**

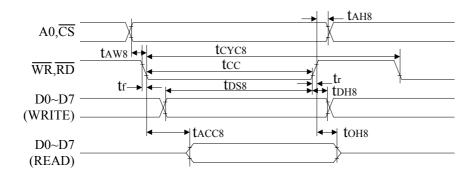

#### MPU Bus Read/Write I (80-Family MPU)

Ta=-20 to 75°C, Vss=-5.0V± 10% unless stated otherwise

| Parameter           | Symbol   | Condition | Rati | ing  | Unit  | Signal                         |

|---------------------|----------|-----------|------|------|-------|--------------------------------|

| Farailleter         | Syllibol | Condition | Min. | Max. | Ollit | Signai                         |

| Address hold time   | tAH8     |           | 10   | -    |       | $A0, \overline{CS}$            |

| Address setup time  | tAW8     |           | 20   | -    |       | 710, C5                        |

| System cycle time   | tCYC8    |           | 1000 | -    |       | DD 1110                        |

| Control pulse width | tcc      |           | 200  | -    |       | $\overline{RD}, \overline{WR}$ |

| Data setup time     | tDS8     |           | 80   | -    | ns    |                                |

| Date hold time      | tDH8     |           | 10   | -    |       | D0 to D7                       |

| RD access time      | tACC8    |           | -    | 90   |       | ולם טו טלו                     |

| Output disable time | tOH8     | CL=100pF  | 10   | 60   |       |                                |

| Rise and fall time  | tr, tf   | -         | -    | 15   |       | -                              |

Vss=-2.7 to -4.5V, Ta=-20 to +75 $^{\circ}$ C

| Parameter           | Symbol | Condition | Rati | ng   | Unit | Signal                            |  |

|---------------------|--------|-----------|------|------|------|-----------------------------------|--|

| Parameter           | Symbol | Condition | Min. | Max. | 5    | Olgilai                           |  |

| Address hold time   | tAH8   |           | 20   | -    |      | $A0, \overline{CS}$               |  |

| Address setup time  | tAW8   |           | 40   | -    |      | A0, C5                            |  |

| System cycle time   | tCYC8  |           | 2000 | -    |      | $\overline{RD}$ , $\overline{WR}$ |  |

| Control pulse width | tcc    |           | 400  | -    |      | KD, WK                            |  |

| Data setup time     | tDS8   |           | 160  | -    | ns   |                                   |  |

| Date hold time      | tDH8   |           | 20   | -    |      | D0 to D7                          |  |

| RD access time      | tACC8  |           | -    | 180  |      | ולם טו טל                         |  |

| Output disable time | tOH8   | CL=100pF  | 20   | 120  |      |                                   |  |

| Rise and fall time  | tr, tf | -         | -    | 15   |      | -                                 |  |

# NT7450B

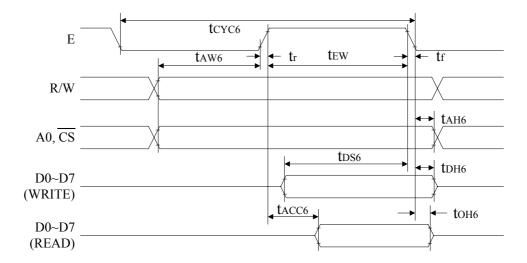

#### MPU Bus Read/Write II (68-Family MPU)

Ta=-20 to 75°C, Vss=-5.0V± 10% unless stated otherwise

| Parameter               | Symbol | Condition  | Rati | ng   | Unit  | Signal                            |  |

|-------------------------|--------|------------|------|------|-------|-----------------------------------|--|

| Parameter               | Symbol | Condition  | Min. | Max. | Ullit | Signal                            |  |

| System cycle time       | tCYC6  |            | 1000 | -    |       |                                   |  |

| Address setup time      | tAW6   |            | 20   | -    |       | $A0,\overline{CS},R/\overline{W}$ |  |

| Address hold time       | tAH6   |            | 10   | -    |       |                                   |  |

| Data setup time         | tDS6   |            | 80   | -    |       |                                   |  |

| Data hold time          | tDH6   |            | 10   | -    | ns    | D0 to D7                          |  |

| Output disable time     | tOH6   | CL =100pE  | 10   | 60   |       | D0 to D7                          |  |

| Access time             | tACC6  | - CL=100pF | -    | 90   |       |                                   |  |

| Enable Pulse Width Read | tEW    |            | 100  | -    |       | E                                 |  |

| Write                   | ι⊑vv   |            | 80   | -    |       | _                                 |  |

| Rise and fall time      | tr, tf | -          | -    | 15   |       | -                                 |  |

Vss=-2.7 to -4.5V, Ta=-20 to +75 $^{\circ}$ C

| Parameter              | Symbol   | Condition | Ratir | ng   | Unit  | Signal                            |  |

|------------------------|----------|-----------|-------|------|-------|-----------------------------------|--|

| Farameter              | Syllibol | Condition | Min.  | Max. | Ollit | Signal                            |  |

| System cycle time      | tCYC6    |           | 2000  | -    |       | 4.0 <u>GG</u> D / <del>III</del>  |  |

| Address setup time     | tAW6     |           | 40    | -    |       | $A0,\overline{CS},R/\overline{W}$ |  |

| Address hold time      | tAH6     |           | 20    | -    |       |                                   |  |

| Data setup time        | tDS6     |           | 160   | -    |       |                                   |  |

| Data hold time         | tDH6     |           | 20    | -    | ns    | D0 to D7                          |  |

| Output disable time    | tOH6     | CL=100pF  | 20    | 120  |       | וט וט טו                          |  |

| Access time            | tACC6    | CL-100pr  | -     | 180  |       |                                   |  |

| Enable Pulse Width Rea | d tEW    |           | 200   | -    |       | E                                 |  |

| Write Width            | e (Evv   |           | 160   | -    |       | _                                 |  |

| Rise and fall time     | tr, tf   | -         | -     | 15   |       | -                                 |  |

Notes: 1.tcyc6 is the cycle time of  $\overline{CS}$ . E=H, not the cycle time of E.

NT7450B

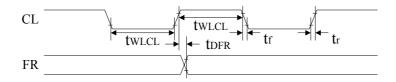

#### **Display Control Signal Timing**

#### Input

Ta=-20 to 75°C, Vss=-5.0V± 10% unless stated otherwise

| Parameter              | Symbol | Condition | Rating |      |      | Unit    | Signal |  |

|------------------------|--------|-----------|--------|------|------|---------|--------|--|

| i didilietei           | Symbol | Condition | Min.   | Тур. | Max. |         | Signal |  |

| Low-level pulse width  | tWLCL  |           | 35     | -    | -    | $\mu$ s |        |  |

| High-level pulse width | tWHCL  |           | 35     | -    | -    | $\mu$ s | CL     |  |

| Rise time              | tr     |           | -      | 30   | 150  | ns      | OL     |  |

| Fall time              | tf     |           | -      | 30   | 150  | ns      |        |  |

| FR delay time          | tDFR   |           | -2.0   | 0.2  | 2.0  | $\mu$ s | FR     |  |

Vss=-2.7 to -4.5V, Ta=-20 to +75 $^{\circ}$ C

| Parameter              | Symbol   | Condition |      | Rating |      |         | Signal |  |

|------------------------|----------|-----------|------|--------|------|---------|--------|--|

| i didilietei           | Syllibol | Condition | Min. | Тур.   | Max. | Unit    | Signal |  |

| Low-level pulse width  | tWLCL    |           | 70   | -      | -    | $\mu$ s |        |  |

| High-level pulse width | tWHCL    |           | 70   | -      | -    | $\mu$ s | CL     |  |

| Rise time              | tr       |           | -    | 60     | 300  | ns      | OL     |  |

| Fall time              | tf       |           | -    | 60     | 300  | ns      |        |  |

| FR delay time          | tDFR     |           | -4.0 | 0.4    | 4.0  | $\mu$ s | FR     |  |

Note: The listed input tDFR applies to the NT7450B and NT7451 in slave mode.

#### **Output**

Ta=-20 to  $75^{\circ}$ C, Vss=-5.0V± 10% unless stated otherwise

| Parameter     | Symbol Condition |           | Rating |      |      | Unit    | Signal |  |

|---------------|------------------|-----------|--------|------|------|---------|--------|--|

| Parameter     | Syllibol         | Condition | Min.   | Тур. | Max. | Oill    | Signal |  |

| FR delay time | tDFR             | CL=100pF  | -      | 0.2  | 0.4  | $\mu$ S | FR     |  |

Vss=-2.7 to -4.5V, Ta=-20 to +75 $^{\circ}$ C

| Parameter     | Symbol Condition |           |      | Rating | J    | Unit    | Signal |  |

|---------------|------------------|-----------|------|--------|------|---------|--------|--|

| Parameter     | Syllibol         | Condition | Min. | Тур.   | Max. | o i i   | Signal |  |

| FR delay time | tDFR             | CL=100pF  | -    | 0.4    | 0.8  | $\mu$ s | FR     |  |

# NT7450B

### **APPLICATION NOTES**

### **MPU Interface Configuration**

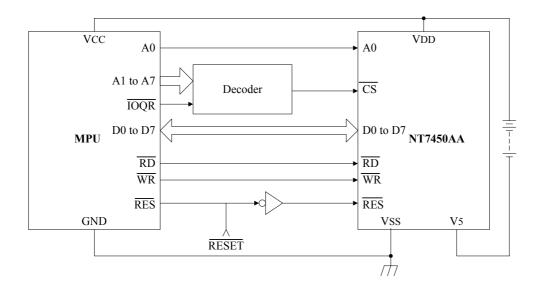

80 Family MPU

# NT7450B

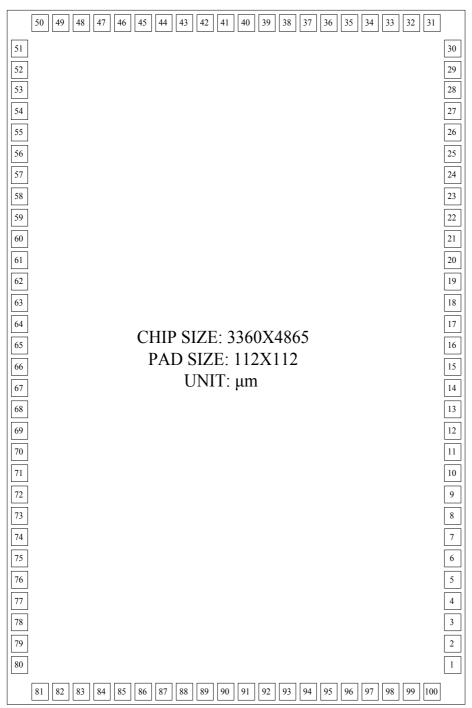

#### **PAD DIAGRAM**

Note: Please connects the substrate to VDD or floating

X,Y(0,0)

# NT7450B

### PAD DIAGRAM (NT7450B)

| Pad No. | Pad name | Х        | Υ        | Pad No. | Pad name  | Х        | Υ        |

|---------|----------|----------|----------|---------|-----------|----------|----------|

| 1       | COM5     | 3334     | 142      | 51      | SEG21     | 540      | 3695     |

| 2       | COM6     | <b>A</b> | 258      | 52      | SEG20     | 105      | 3649     |

| 3       | COM7     | T        | 383      | 53      | SEG19     | <b>A</b> | 3524     |

| 4       | COM8     |          | 508      | 54      | SEG18     | T        | 3399     |

| 5       | COM9     |          | 633      | 55      | SEG17     |          | 3274     |

| 6       | COM10    |          | 758      | 56      | SEG16     |          | 3149     |

| 7       | COM11    |          | 883      | 57      | SEG15     |          | 3024     |

| 8       | COM12    |          | 1008     | 58      | SEG14     |          | 2899     |

| 9       | COM13    |          | 1133     | 59      | SEG13     |          | 2774     |

| 10      | COM14    |          | 1258     | 60      | SEG12     |          | 2649     |

| 11      | COM15    |          | 1383     | 61      | SEG11     |          | 2524     |

| 12      | SEG60    |          | 1508     | 62      | SEG10     |          | 2399     |

| 13      | SEG59    |          | 1633     | 63      | SEG9      |          | 2274     |

| 14      | SEG58    |          | 1758     | 64      | SEG8      |          | 2149     |

| 15      | SEG57    |          | 1883     | 65      | SEG7      |          | 2024     |

| 16      | SEG56    |          | 2008     | 66      | SEG6      |          | 1899     |

| 17      | SEG55    |          | 2133     | 67      | SEG5      |          | 1774     |

| 18      | SEG54    |          | 2258     | 68      | SEG4      |          | 1649     |

| 19      | SEG53    |          | 2383     | 69      | SEG3      |          | 1524     |

| 20      | SEG52    |          | 2508     | 70      | SEG2      |          | 1399     |

| 21      | SEG51    |          | 2633     | 71      | SEG1      |          | 1274     |

| 22      | SEG50    |          | 2758     | 72      | SEG0      |          | 1149     |

| 23      | SEG49    |          | 2883     | 73      | A0        |          | 1024     |

| 24      | SEG48    |          | 3008     | 74      | cs_       |          | 899      |

| 25      | SEG47    |          | 3133     | 75      | CL        |          | 774      |

| 26      | SEG46    |          | 3258     | 76      | E/RD      |          | 649      |

| 27      | SEG45    |          | 3383     | 77      | R/W/ (WR) |          | 524      |

| 28      | SEG44    |          | 3508     | 78      | GND       |          | 399      |

| 29      | SEG43    | ▼        | 3633     | 79      | DB0       | ▼        | 274      |

| 30      | SEG42    | 3165     | 3695     | 80      | DB1       |          | 149      |

| 31      | SEG41    | 3040     | <b>1</b> | 81      | DB2       | 308      | 105      |

| 32      | SEG40    | 2915     | 1 T      | 82      | DB3       | 440      | <b>A</b> |

| 33      | SEG39    | 2790     | 1        | 83      | DB4       | 572      |          |

| 34      | SEG38    | 2665     | 1        | 84      | DB5       | 704      |          |

| 35      | SEG37    | 2540     | ]        | 85      | DB6       | 836      |          |

| 36      | SEG36    | 2415     | ]        | 86      | DB7       | 968      |          |

| 37      | SEG35    | 2290     | ]        | 87      | $V_{CC}$  | 1100     |          |

| 38      | SEG34    | 2165     | ]        | 88      | RES       | 1232     |          |

| 39      | SEG33    | 2040     | ]        | 89      | FR        | 1364     |          |

| 40      | SEG32    | 1915     |          | 90      | V5        | 1496     |          |

| 41      | SEG31    | 1790     | ]        | 91      | V3        | 1628     |          |

| 42      | SEG30    | 1665     | ]        | 92      | V2        | 1760     |          |

| 43      | SEG29    | 1540     | ]        | 93      | M/S       | 1892     |          |

| 44      | SEG28    | 1415     | ]        | 94      | V4        | 2024     |          |

| 45      | SEG27    | 1290     | ]        | 95      | V1        | 2156     |          |

| 46      | SEG26    | 1165     | ]        | 96      | COM0      | 2288     |          |

| 47      | SEG25    | 1040     | ]        | 97      | COM1      | 2420     |          |

| 48      | SEG24    | 915      | ]        | 98      | COM2      | 2552     |          |

| 49      | SEG23    | 790      | 」        | 99      | COM3      | 2684     | ₩        |

| 50      | SEG22    | 665      | •        | 100     | COM4      | 2816     | •        |