# ST20P08 8K 8-bit Single Chip Microcontroller

Notice: Sitronix Technology Corp. reserves the right to change the contents in this document without prior notice. This is not a final specification. Some parameters are subject to change.

### **1. FEATURES**

- 8-Bit Static Pipeline CPU

- ROM: 8K x 8 bits PROM(OTP)

- RAM: 192 x 8 bits

- 32-Level Deep Stack

- Operating Voltage : 2.4V ~ 5.5V

- Power-on Timer(PWRT)

- Pin option to enable

- General-Purpose I/O (GPIO) Ports

- 28 pins are programmable CMOS I/O (Port-A/B/C and Port-E low nibble),20 pins (Port-A high nibble & Port-B/C) are shared with LCD Segments

- 8 open drain output pins share with LCD COMs

- Hardware de-bounce option for Port-A

- Bit programmable pull-up for input pins

- 2 Input Pins

- OTP option bit to select (shared with OSCX)

- 30 Output Pins

- Eight are shared with LCD com and twenty are shared with LCD Segments, two are shared with PSG

- Timer / Counter

- One 8-bit timer / 16-bit event counter

- One 8-bit BASE timer

- Five Powerful Interrupt Sources

- External interrupt (edge trigger) / RFC interrupt(Share with external interrupt)

- TIMER1 interrupt

- BASE timer interrupt

- PORTA[7~0] interrupt (transition trigger)

- DAC reload interrupt

#### Watchdog Timer (WDT)

- With its own low power internal oscillator for reliability

- Four selectable time bases

- WDT reset CPU only

- OTP option bit to enable

- One option bit is selectable to reset or not in WAI1 and STP mode

- Dual Clock Source with Warm-up Timer

- OSCX: Low frequency crystal oscillator with 32768Hz

- OSC: High frequency RC oscillator from 500K ~ 8MHz

- CPU clock 250K ~ 4MHz

- **On-chip Internal Oscillator for WDT**

- < 5uA typical, 3V, 27°C

- LCD Controller Driver

- 16 level contrast control

- 320 (8x40) dots (1/8 duty, 1/4 bias, programmable)

- 160 ( 4x40) dots ( 1/4 duty, 1/3 bias, programmable)

- Two clock source options: RC and resonator oscillator

- Keyboard scan function supported on 40 shared segment drives

- Internal bias resistors(1/4 bias & 1/3 bias) with 32 level driving strength control

- Programmable Sound Generator (PSG)

- Tone generator

- Sound effect generator

- 16 level volume control

- Digital DAC for speech / tone

- Resistor Frequency Converter (RFC)

- Up to 4 resistors measurement

- Built-in one independent 16-bits counter without sharing with timer counter

- 3 clock sources for RFC counter: SYSCK, OSCX and INTX

- 5 scales of clock divider for RFC counter

- Carrier Wave Generator(CGR)

- Built-in one digital PLL

- Standard clock rate output for remote control

- Three Power Down Modes

- WAI0 mode

- WAI1 mode

- STP mode

## 2. GENERAL DESCRIPTION

ST20P08 is a low-cost, high-performance, fully static, 8-bit microcontroller designed with CMOS silicon gate technology. It comes with 8-bit pipeline CPU core, SRAM, timer, LCD driver, I/O port, PSG, RFC, CGR, OTP program ROM and built-in dual oscillator. And also, some new functions have been added in the ST20P08 to enhance the performance of ST2016 for more system application.

Power bouncing during power-on is a major problem when designing a reliable system. After the power returns to normal level, the system may recover its original states and keeps working correctly. Furthermore, the Power-on Timer (PWRT) which is designed to provide a fixed delay time, keep the part in reset for longer after power-up or low-V reset released. With these two power management, the system may operate under more stabile power supply.

A highly reliable Watchdog Timer(WDT) with its own low power internal oscillator which does not require any external components, provides protection against software lockup. Moreover, the feature of "WDT reset CPU only" make it possible to do the rapid system recovery after Watchdog timer reset. And the option bit is selectable to reset or not in WAI1 and STP mode for various application. The Resistor Frequency Converter(RFC) which is also a new function added in the ST20P08, can compare three different sensors with the reference resistor separately. With one independent 16-bits counter, the RFC can count and stop automatically only if RFC is enabled. This make it easy for the humidity or thermometric application.

More and more remote control applications are used today. The ST20P08 also equips a Carrier Wave Generator(CGR) to support this application with one digital PLL and provide the standard clock rates output for remote control.

With these integrated functions inside, the ST20P08 single chip microcontroller is a right solution for business equipment and consumer applications. Such as watch, calculator, LCD games, thermometer, hygrometer, IR remote control and so on. ST20P08 is definitely a perfect solution for implementation.

ST20P08

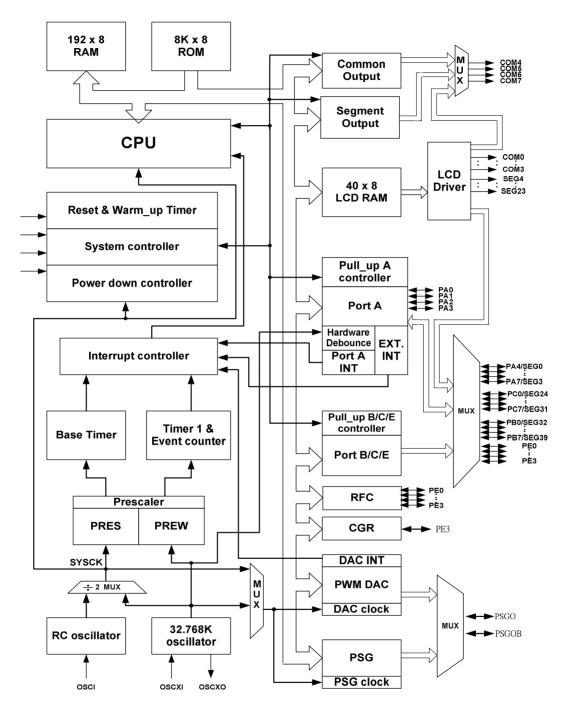

### 3. BLOCK DIAGRAM

#### ST20P08

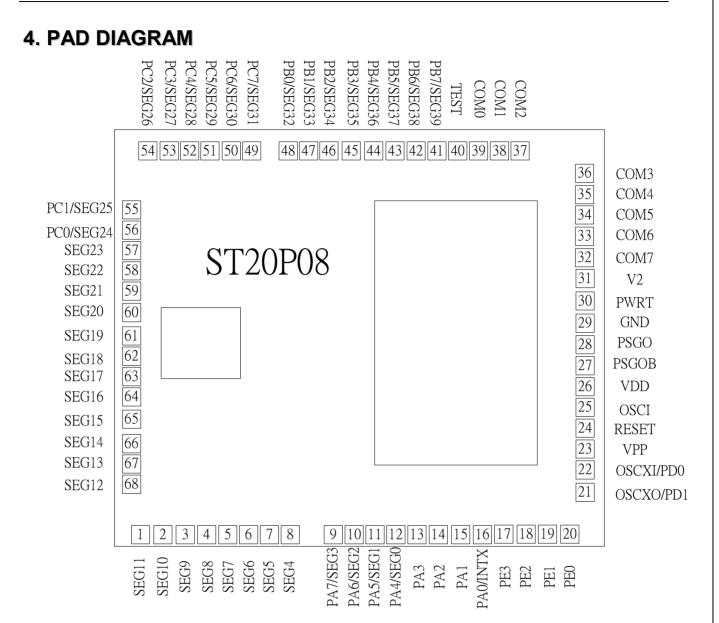

# 5. PAD DESCRIPTION

| Pin No.    | Designation              | Туре               | Description                                                                                                                |

|------------|--------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| 12~9       | SEG0/PA4 ~<br>SEG3/PA7   | 0<br>I/O           | LCD Segment output<br>Port-A bit programmable I/O                                                                          |

| 8~5        | SEG4- SEG7               | 0                  | LCD Segment output<br>Segment output port                                                                                  |

| 4~1, 68~65 | SEG8 -SEG15              | 0                  | LCD Segment output<br>Segment output port                                                                                  |

| 64~57      | SEG16-SEG23              | 0                  | LCD Segment output<br>Segment output port                                                                                  |

| 56~49      | SEG24/PC0 ~<br>SEG31/PC7 | 0<br>I/O           | LCD Segment output<br>Port-C bit programmable I/O                                                                          |

| 48~41      | SEG32/PB0 ~<br>SEG39/PB7 | 0<br>I/O           | LCD Segment output<br>Port-B bit programmable I/O                                                                          |

| 39~32      | COM 0 – 7                | 0<br>0             | LCD Common output<br>Open drain output port                                                                                |

| 24         | RESET                    | I                  | Pad reset input (HIGH Active)                                                                                              |

| 29         | GND                      | Р                  | Ground Input and chip substrate                                                                                            |

| 16         | PA0/INTX                 | I/O<br>I<br>I<br>I | Port-A bit programmable I/O<br>Edge-trigger Interrupt.<br>Transition-trigger Interrupt<br>Programmable Timer1 clock source |

| 15~9       | PA 1-7                   | I/O<br>I           | Port-A bit programmable I/O<br>Transition-trigger Interrupt                                                                |

| 28~27      | PSGO,PSGOB               | 0                  | PSG/DAC Output                                                                                                             |

| 26         | VDD                      | Р                  | Power supply                                                                                                               |

| 22         | OSCXI/PD0                |                    | OSC input pin. For 32768Hz crystal<br>Port-D input                                                                         |

| 21         | OSCXO/PD1                | 0<br>I             | OSC output pin. For 32768Hz<br>crystal<br>Port-D input                                                                     |

| 25         | OSCI                     | I                  | OSC input pin. Toward to external resistor                                                                                 |

| 20~17      | PE0~PE3                  | I/O                | Port-E bit programmable I/O<br>RFC/CGR output                                                                              |

| 31         | V2                       | 0                  | Multi-level power supply for liquid crystal drive.                                                                         |

| 23         | VPP                      | Р                  | OTP programming power                                                                                                      |

| 40         | TEST                     | I                  | Chip test function. Leave it open                                                                                          |

| 30         | PWRT                     | I                  | Power on timer enable control pin.                                                                                         |

Legend: I = input, O = output, I/O = input/output, P = power.

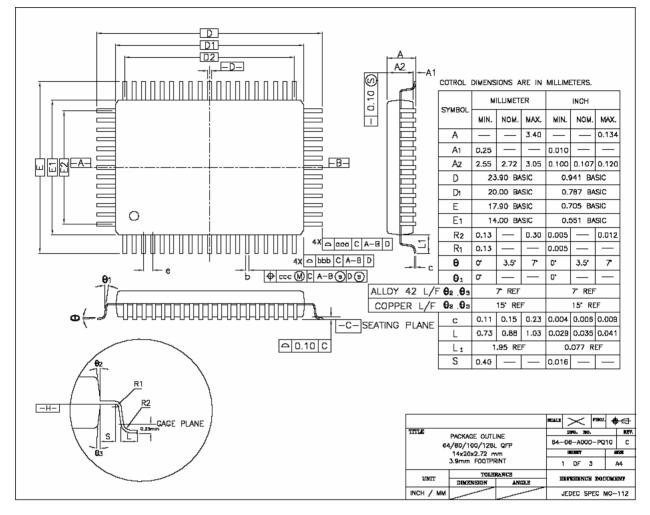

## 6. PACKAGE DIMENSIONS

#### **Dimensions in Millimeters**

|          | 80L        |                                 |      |  |  |  |  |  |

|----------|------------|---------------------------------|------|--|--|--|--|--|

| SYMBOL   | MILLIMETER |                                 |      |  |  |  |  |  |

| STIVIDUL | MIN.       | MIN. NOM.                       |      |  |  |  |  |  |

| b        | 0.30       | 0.35                            | 0.45 |  |  |  |  |  |

| е        |            | 0.80 BSC.                       |      |  |  |  |  |  |

| D2       | 18.4 REF   |                                 |      |  |  |  |  |  |

| E2       | 12.0 REF   |                                 |      |  |  |  |  |  |

|          | TOLEREANC  | TOLEREANCE OF FORM AND POSITION |      |  |  |  |  |  |

| aaa      | 0.25       |                                 |      |  |  |  |  |  |

| bbb      | 0.20       |                                 |      |  |  |  |  |  |

| CCC      | 0.20       |                                 |      |  |  |  |  |  |

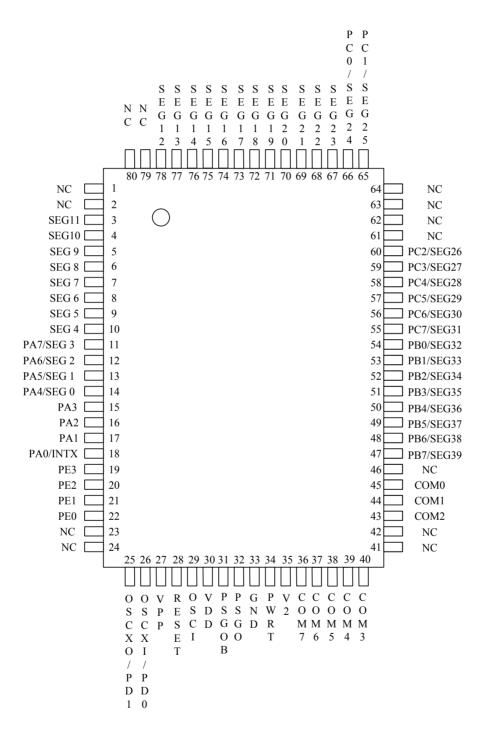

## 7. PIN CONFIGURATION(QFP80)

# 8. Application Circuits

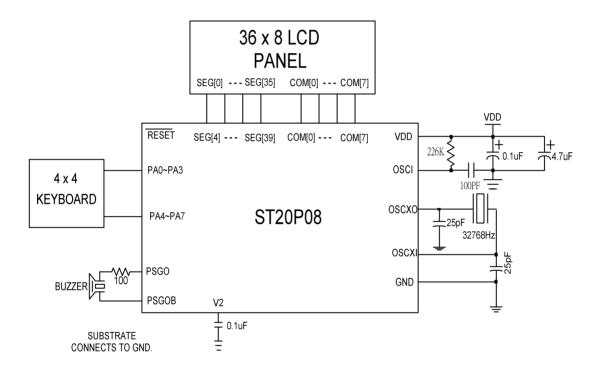

#### 8.1 APPLICATION CIRCUIT UNDER 3V OPERATING VOLTAGE

| VDD   | : 3V                                       |

|-------|--------------------------------------------|

| Clock | : 32768Hz crystal and 4.0MHz RC oscillator |

| LCD   | : 1/8 duty                                 |

| I/O   | : PORT A                                   |

| ALARM | : PSGO. PSGOB                              |

#### FIGURE 8-1: APPLICATION CIRCUIT WITHOUT LCD KEYBOARD AWAKING PULSE

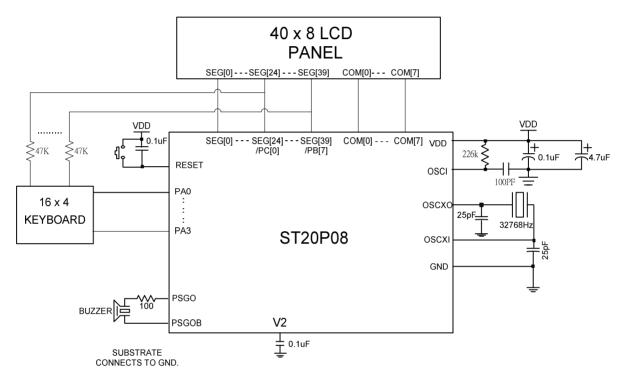

| VDD   | : 3V                                       |

|-------|--------------------------------------------|

| Clock | : 32768Hz crystal and 4.0MHz RC oscillator |

| LCD   | : 1/8 duty                                 |

| I/O   | : PORT A                                   |

| ALARM | : PSGO, PSGOB                              |

|       |                                            |

FIGURE 8-2: APPLICATION CIRCUIT WITH LCD KEYBOARD AWAKING PULSE

Note:

- 1. COMs and SEGs output GND level, while the LCD is turned off.

- 2. If LCD is turned off, Keyboard Awaking Pulses must be turned off at the same time.

- 3. Connect one capacitor of 100PF to OSCI stabilize oscillation frequency. This capacitor must be placed close to OSCI.

## 9. OTP ROM Programming Interface

#### **Interface Description** 9.1

In order to program OTP ROM, several pins have to be reserved on the PCB which is bounding with ST20P08. These total are 8 pins that include following list TABLE 9-1: . It just be used to connect writer to program OTP ROM. After programming and disconnecting from writer, they can be used as original purpose.

| P18 Pad Name | (SPI Interface) | Pin Type | Description                                                                                                                                |

|--------------|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| VPP          | VPP             | Power    | <ul> <li>High Voltage Power Supply</li> <li>1) OTP Program, Program Verify, VPP=&gt; 12V</li> <li>2) OTP Read:VPP=&gt; Floating</li> </ul> |

| GND          | VSS             | Power    | Ground.                                                                                                                                    |

| VCC          | VDD             | Power    | Low Voltage (2.4V-5.4V) Power Supply.                                                                                                      |

| PE3          | SSB             | Input    | SPI signal                                                                                                                                 |

| SEG4         | MOSI            | Input    | SPI signal                                                                                                                                 |

| SEG5         | MISO            | Output   | SPI signal                                                                                                                                 |

| PE2          | SCK             | Input    | SPI signal                                                                                                                                 |

| RESET        | RESET           | Input    | SPI RESET                                                                                                                                  |

#### - -.

#### 9.2 **Programming Function Specification**

There are reserved 5 option bits to select to apply or not the function we needed. It includes PD input, WDT enable, WDT stop at WAI-1 and Code Protection. To setup the

options should program the OTP ROM by OTP writer by control register. The register OTP(\$37) is used to read contents of the option word.

ST20P08

|                                                                                                                                                                                                                                     | TABLE 9-2:     Option ward                                                                                         |       |       |        |                         |   |                |        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-------|--------|-------------------------|---|----------------|--------|--|--|

| Bit 7                                                                                                                                                                                                                               | Bit 6                                                                                                              | Bit 5 | Bit 4 | Bit 3  | Bit 3 Bit 2 Bit 1 Bit 0 |   | Bit 1 Bit 0 De |        |  |  |

| СР                                                                                                                                                                                                                                  | -                                                                                                                  | -     | -     | WDTSTP | WDTEN                   | - | PD             | 1 11-1 |  |  |

| Bit 7: <b>CP</b> : OTP ROM code protect.<br>0 =protect OTP data.<br>1 =Un-Protect OTP data.<br>Bit 3: <b>WDTSTP</b> : WDT stop control bit.<br>0 = WDT stop at WAI-1 and STP mode.<br>1 = WDT is always active if WDTEN is enabled. |                                                                                                                    |       |       |        |                         |   |                |        |  |  |

| Bit 2: <b>WDTEN</b> : WDT enable.<br>0 = WDT disable.<br>1 = WDT enable.                                                                                                                                                            |                                                                                                                    |       |       |        |                         |   |                |        |  |  |

|                                                                                                                                                                                                                                     | Bit 0: <b>PD</b> : Port function selection<br>0 = PD used as input port.<br>1 = OSC input pin for 32768Hz crystal. |       |       |        |                         |   |                |        |  |  |

TABLE 9-3:

OTP option ward read back window

| Address | Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Default |

|---------|------|-----|-------|-------|-------|-------|--------|-------|-------|-------|---------|

| \$037   | ΟΡΤ  | R   | СР    | -     | -     | PWRT  | WDTSTP | WDTEN | -     | PD    | 11 11-1 |

## 10. Power On Timer

The Power-on Timer (PWRT) is offered necessary delays on power-up to keep the chip in reset until the crystal oscillator is stable, the typical delay time in 3v at 25  $^\circ C$  is

32ms, and operation in voltage 2.4V~5.5V ,60  $^\circ\text{C}$  ~ -10 $^\circ\text{C}$  is 4~640ms. The default state is high with one internal pull-up resistance.

| IC pad | option | Description                        | Default         |

|--------|--------|------------------------------------|-----------------|

| PWRT   | 0      | disable power-on timer, tie to GND | 1:input pull-up |

| FWINI  | 1      | enable power-on timer, tie to VCC  | 1.input puil-up |

ST20P08

ST20P08 EVB PCB113-2

TABLE 10-5: The PCB 113-2 of ST20P08 EVB

ST20P08

# 11. Revisions

| REVISION | DESCRIPTION               | PAGE | DATE    |

|----------|---------------------------|------|---------|

| 01       | First release             | 1~12 | 5/23/06 |

| 0.2      | Add CPU clock 250K ~ 4MHz | 1    | 6/23/06 |

| 0.3      | Add EVB photo             | 12   | 5/23/07 |

|          |                           |      |         |

|          |                           |      |         |

The above information is the exclusive intellectual property of Sitronix Technology Corp. and shall not be disclosed, distributed or reproduced without permission from Sitronix. Sitronix Technology Corp. reserves the right to change this document without prior notice and makes no warranty for any errors which may appear in this document. Sitronix products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where products failure could result in injury, or loss of life, or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.